ECE/CS 3710

Fall 2009

|

|

|

|

| General Information: |

| Title: | ECE/CS 3710 - Computer Design Lab - Fall 2009 |

| Instructor: | Ken Stevens, kstevens@ece.utah.edu, MEB 4506, 585-9176 |

| Classes: | Tue & Thu 3:40pm - 5:00pm, Lectures in WEB 110 |

| Labs: | Labs in School of Computing DSL (MEB 3133) |

| Office Hours: | by appointment |

| Web Page: | www.eng.utah.edu/~kstevens/3710/3710.html |

| TA: | William Lee, teach-3710@list.eng.utah.edu |

| TA Hours: | TBD |

| Text Book | None. There will be handouts. |

| Prerequisites: | ECE/CS 3700 (digital design) and ECE/CS 3810 (computer architecture) or equivalent |

| Course Description: |

This is a laboratory class in which groups of students (of size 3 or 4) design, build, and test a simple computer. The idea is to use your digital design skills from 3700 and your computer architecture knowledge from 3810, and put it all together into an interesting semester-long project. You will receive the design specifications in lectures. You will then interpret the specifications and develop a model of the design using a combination of Verilog and schematics. The model should be simulated. Once validated you will synthesize the design onto the FPGA boards. The design will contain the instruction set design, memory organization, ALU design, control, and input-output design.

We are going to implement a "simpler" model of the CR16A Microprocessor (more details below). You will receive a baseline instruction set that every team will have to implement. Subsequently, each team will augment their instruction set depending upon the type of applications they have in mind.

In addition to the basic processor design, each student team will develop I/O + memory interfaces, along with necessary drivers that will control the interfaces. Moreover, each team will propose further extensions to their designs for particular targeted applications. You will have enough leverage to come up with your own applications and extensions. For example, you can develop games, do some graphics/visualization (VGA interfaces), audio signal processing (interfacing audio CODECs), study and implement basic pipelining, or design fast/efficient arithmetic components. The choice is yours. Make sure that your extensions somehow relate to your applications, and make it a lot of fun!

One of the main deliverable of this class is to design an application to run on your processor. Many students have designed games as the software that runs on the CPU. These have included a game of skiers trying to ski down a slope while avoiding obstacles, rock-paper-scissors, ping-pong, tank battlefield, among many other configurable and modular games. Students have also designed music synthesizers, applications to control stepper motors and such. Sometime around the first/second week of October, each group of students will need to decide on an application.

We will have a mid-semester presentation on what you have done so far (what, how, why, problems faced, workarounds, etc.) and what application you intend to design on your CPU. Once you have defined your project, you will proceed towards writing assemblers + software for your code. Each group, and every member of the group will have to make a presentation to the class.

Lectures:

This is a primarily a lab class. Although there are lectures scheduled on Tuesday and Thursday from 3:40pm - 5:00pm, the main point of the class is the project. The lectures will present material related to the project, and there will be TA hours held in the digital systems lab (DSL) (MEB 3133) both so that you can get help from the TA, and also to check off project milestones.

Course Deliverables:

You will submit a final report at the end of the semester, make a presentation to the class as well as visitors, and demonstrate a functioning design. There may be one exam, probably some time towards the end of the semester, to make sure that every team member has a good understanding of what's going on in the class.

Course Mailing Lists:

There are two class mailing lists: 3710@list.eng.utah.edu and teach-3710@list.eng.utah.edu. The 3710 list will be used to send out important information to everyone in the class. Please use discretion when sending messages to the entire class. Mail sent to teach-3710 just goes to the instructor and TA. This is the preferred method of communicating with the TA and instructor.

The lists were automatically populated with your university mailing address. If you would like to add another e-mail address, you can send a subscribe request by logging on to the UofU sympa mailing list server. Let me know if you would like to remove your university e-mail address in lieu of another preferred address.

| Grading Policy: |

| Incomplete Policy: | You can't get an incomplete unless you have a documented medical or legal emergency. |

| College Guidelines: | Refer to the college policy on adding and dropping classes, etc. |

| Disability: | If you have a condition that merits consideration, you must contact the instructor at the beginning of the course. |

| Labs and checkpoints: | 35% |

| Mid-semester presentation: | 10% |

| Final Project: | 45% |

| Final Exam | 10% |

The final project grade is split between the written documentation, project meeting the proposed functionality, and team member evaluation.

The documentation should be written as a technical paper suitable for publication in a conference or journal. Look here for details on the requirements for your project report.

| Homework Assignments and Labs: |

| Date Due | Description |

| Sept 3rd | Review Quiz This assignment will cover material that you should have learned in ECE/CS 3700 and ECE/CS 3810. If you can't remember this stuff, these are the areas where you need to refresh your memory. If you have no idea about this stuff, you'll struggle in the class! |

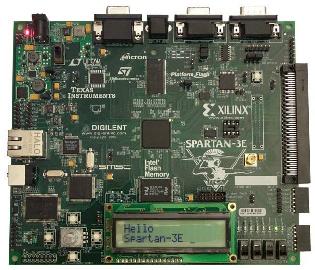

| Sept 10th | Finite State Machine Lab T-bird Turn Signals mapped to the Spartan-3E board This is the same T-bird assignment as last semester in 3700, but mapped to the Spartan-3E board. Check out the tutorial on using ISE 10.1 with the Spartan-3E board. There are other tutorials that may help you on the ECE/CS 3700 web site. |

| Sept 22nd | Tiny MIPS processor In this lab you'll use the mips.v code from CMOS VLSI Design by Weste and Harris. You'll also want to use exmem.v which is Verilog code that describes memory that can be implemented as block RAM on the Spartan-3E part. You will use the assembly program fibn.asm that computes the n-th Fibonacci number, and the corresponding fib.dat file with the machine encoded version that you can use to load the Block RAM. The details of this MIPS processor are found in Section 1.7 of CMOS VLSI Design. Hard copies of that section of the book will be handed out in class. Following are the primary deliverables and modifications for this lab:

|

| Sept 22nd | Declare project groups Turn in your group information described in the assignment either by email to teach-3710@list.eng.utah.edu or in class. |

| TBD | Checkpoints From here on out you'll be working in groups on your processor projects. Group meetings will be scheduled to monitor your progress. You'll need to check off a series of checkpoints to demonstrate that progress. There isn't a specific schedule on these checkpoint so that your group can set your own timetable, but if you start falling behind specific time tables will be put into place on a per-group basis.

|

| Oct 27 | Project Proposal Proposal Presentation You will turn in your proposal that describes your deliverables for the semester. We will also schedule a presentation on their proposed project to the class. |

| Dec 11+ | Final Report and Demo There are three parts to the final report:

|

| Dec 11 | Group Evaluation Form This is a confidential form you use to evaluate you and your group in terms of everyone's contribution to the team. Every group member must fill out their own copy of the form and turn it in separately. Be honest and frank in your confidential evaluation of your team members. You can turn it in via email to teach-3710 or by hard copy to the instructor or TA. |

| Dec 16 | Class Evaluation Form This is a form you can use to give me confidential feedback on how you think the class went this semester. Let me know what you liked and didn't like, what worked, and what could have worked better. You don't need to sign this form! You can turn it in to the ECE office, or slip it under my office door. |

| Lecture Notes: |

Introduction to ECE/CS 3710

Introduction to ECE/CS 3710

Introduction to the

Spartan 3E FPGA

Introduction to the

Spartan 3E FPGA

Verilog Refresher

Verilog Refresher

The Mini-MIPS architecture

The Mini-MIPS architecture

The CR-16 architecture project for this semester

The CR-16 architecture project for this semester

Some more Verilog synthesis examples to help with your project

Some more Verilog synthesis examples to help with your project

A review of displays and the VGA Standard, and support on the Spartan 3E

A review of displays and the VGA Standard, and support on the Spartan 3E

Other Spartan 3E I/O support you may want to use in your project

Other Spartan 3E I/O support you may want to use in your project

| Team Assignments: |

Following are the team assignments for team lab assignments and class meetings and presentations:

| Networked Messaging | Travis Jeppson, Kevin Jones, Ben Martin |

| Battleship | Landon Anderson, Alex Freshman, Kameron Sheffield |

| Mountain Ray | Johnathan Davies, Kevin Faerber, Long Nguyen, Tyler Patterson |

| TeamStroyers | Sanghyun Park, Matt Strum, Michael Yang |

| DDR-SDRAM | Grant Ayers, Nick McDonald |

| RationalRedicals | Christopher Johnson, Jordan Squire, Jens Thompsen, Jake Willoughby |

| Useful Links: |