# HSIM<sup>plus</sup>® Reference Manual

Version C-2009.06, June 2009

# **SYNOPSYS**<sup>®</sup>

# **Copyright Notice and Proprietary Information**

Copyright © 2009 Synopsys, Inc. All rights reserved. This software and documentation contain confidential and proprietary information that is the property of Synopsys, Inc. The software and documentation are furnished under a license agreement and may be used or copied only in accordance with the terms of the license agreement. No part of the software and documentation may be reproduced, transmitted, or translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of Synopsys, Inc., or as expressly provided by the license agreement.

#### **Right to Copy Documentation**

The license agreement with Synopsys permits licensee to make copies of the documentation for its internal use only. Each copy shall include all copyrights, trademarks, service marks, and proprietary rights notices, if any. Licensee must assign sequential numbers to all copies. These copies shall contain the following legend on the cover page:

"This document is duplicated with the permission of Synopsys, Inc., for the exclusive use of \_\_\_\_\_\_ and its employees. This is copy number \_\_\_\_\_\_."

#### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

#### Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### **Registered Trademarks (®)**

Synopsys, AMPS, Astro, Behavior Extracting Synthesis Technology, Cadabra, CATS, Certify, CHIPit, Design Compiler, DesignWare, Formality, HDL Analyst, HSIM, HSPICE, Identify, iN-Phase, Leda, MAST, ModelTools, NanoSim, OpenVera, PathMill, Physical Compiler, PrimeTime, SCOPE, Simply Better Results, SiVL, SNUG, SolvNet, Syndicated, Synplicity, the Synplicity logo, Synplify, Synplify Pro, Synthesis Constraints Optimization Environment, TetraMAX, UMRBus, VCS, Vera, and YIELDirector are registered trademarks of Synopsys, Inc.

#### Trademarks (™)

AFGen, Apollo, Astro-Rail, Astro-Xtalk, Aurora, AvanWaves, BEST, Columbia, Columbia-CE, Confirma, Cosmos, CosmosLE, CosmosScope, CRITIC, CustomSim, DC Expert, DC Professional, DC Ultra, Design Analyzer, Design Vision, DesignerHDL, DesignPower, DFTMAX, Direct Silicon Access, Discovery, Eclypse, Encore, EPIC, Galaxy, Galaxy Custom Designer, HANEX, HAPS, HapsTrak, HDL Compiler, Hercules, Hierarchical Optimization Technology, High-performance ASIC Prototyping System, HSIM<sup>plus</sup>, i-Virtual Stepper, IICE, in-Sync, iN-Tandem, Jupiter, Jupiter-DP, JupiterXT, JupiterXT-ASIC, Liberty, Libra-Passport, Library Compiler, Magellan, Mars, Mars-Rail, Mars-Xtalk, Milkyway, ModelSource, Module Compiler, MultiPoint, Physical Analyst, Planet, Planet-PL, Polaris, Power Compiler, Raphael, Saturn, Scirocco, Scirocco-i, Star-RCXT, Star-SimXT, System Compiler, System Designer, Taurus, TotalRecall, TSUPREM-4, VCS Express, VCSi, VHDL Compiler, VirSim, and VMC are trademarks of Synopsys, Inc.

#### Service Marks (sm)

MAP-in, SVP Café, and TAP-in are service marks of Synopsys, Inc.

SystemC is a trademark of the Open SystemC Initiative and is used under license. ARM and AMBA are registered trademarks of ARM Limited. Saber is a registered trademark of SabreMark Limited Partnership and is used under license. All other product or company names may be trademarks of their respective owners.

Printed in the U.S.A.

|    | Audience                                                                                                                                                                                                          | i                                                        |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|    | Related Publications                                                                                                                                                                                              | i                                                        |

|    | Conventions                                                                                                                                                                                                       | i                                                        |

|    | Customer Support                                                                                                                                                                                                  | ii                                                       |

| 1. | Introduction                                                                                                                                                                                                      | 1                                                        |

|    | HSIM <sup>plus</sup>                                                                                                                                                                                              | 1                                                        |

|    | HSIM <sup>plus</sup> Features                                                                                                                                                                                     | 2                                                        |

|    | HSIM                                                                                                                                                                                                              | 4                                                        |

|    | Interactive Circuit Analysis                                                                                                                                                                                      | 5                                                        |

|    | Applications                                                                                                                                                                                                      | 5                                                        |

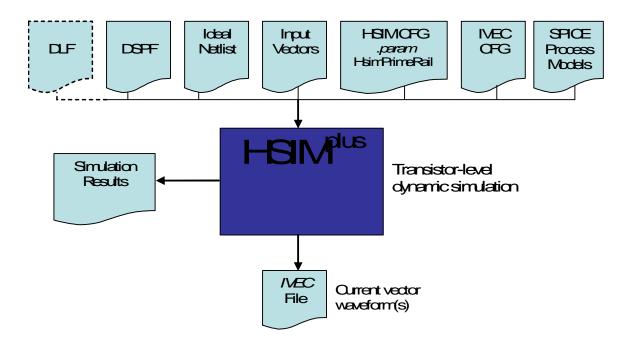

|    | Input/Output Data                                                                                                                                                                                                 | 6                                                        |

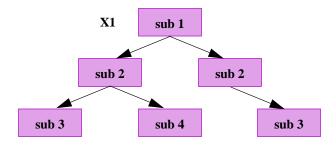

|    | Hierarchical Simulation Technology                                                                                                                                                                                | 6<br>7                                                   |

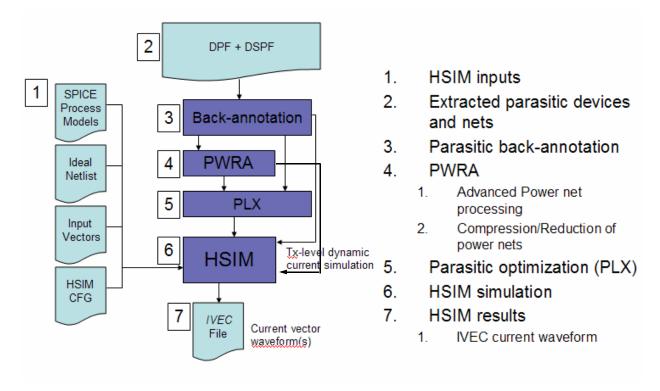

| 2. | Post-Layout Acceleration (PLX) and SP2DSPF Utility                                                                                                                                                                | 9                                                        |

|    | Back-Annotation Without Post-Layout Acceleration                                                                                                                                                                  | 9                                                        |

|    |                                                                                                                                                                                                                   |                                                          |

|    | HSIM <sup>plus</sup> Back-Annotation with Post-Layout Acceleration                                                                                                                                                | 11<br>12                                                 |

|    | -                                                                                                                                                                                                                 |                                                          |

|    | HSIMPFPLX                                                                                                                                                                                                         | 12                                                       |

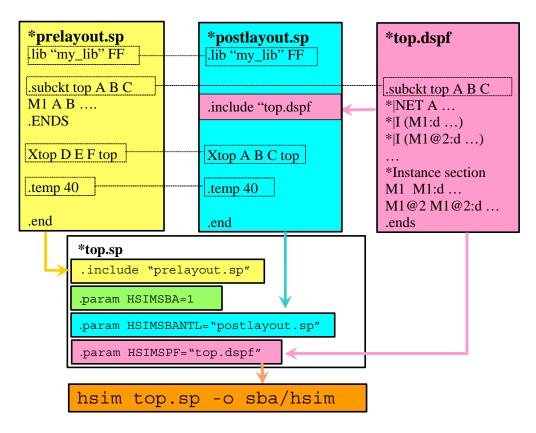

|    | HSIMPFPLX.<br>HSIM <sup>plus</sup> Structural Back-Annotation (SBA)<br>Invoking SBA<br>SBA Parameters                                                                                                             | 12<br>12<br>17<br>18                                     |

|    | HSIMPFPLX.<br>HSIM <sup>plus</sup> Structural Back-Annotation (SBA)                                                                                                                                               | 12<br>12<br>17<br>18<br>18                               |

|    | HSIMPFPLX.<br>HSIM <sup>plus</sup> Structural Back-Annotation (SBA)<br>Invoking SBA<br>SBA Parameters                                                                                                             | 12<br>12<br>17<br>18                                     |

|    | HSIMPFPLX.<br>HSIM <sup>plus</sup> Structural Back-Annotation (SBA)<br>Invoking SBA<br>SBA Parameters<br>HSIMSBA<br>HSIMSBA                                                                                       | 12<br>12<br>17<br>18<br>18<br>18                         |

|    | HSIMPFPLX.<br>HSIM <sup>plus</sup> Structural Back-Annotation (SBA)<br>Invoking SBA<br>SBA Parameters<br>HSIMSBA<br>HSIMSBANTL<br>HSIMSBAPARAM<br>HSIMSBAMSGLEVEL<br>HSIMSBAMSGLIMIT                              | 12<br>12<br>17<br>18<br>18<br>19<br>19<br>22<br>22       |

|    | HSIMPFPLX.<br>HSIM <sup>plus</sup> Structural Back-Annotation (SBA)<br>Invoking SBA<br>SBA Parameters<br>HSIMSBA<br>HSIMSBA<br>HSIMSBANTL<br>HSIMSBAPARAM<br>HSIMSBAMSGLEVEL<br>HSIMSBAMSGLIMIT<br>HSIMSBAHIERID. | 12<br>12<br>17<br>18<br>18<br>19<br>19<br>22<br>22<br>23 |

|    | HSIMPFPLX.<br>HSIM <sup>plus</sup> Structural Back-Annotation (SBA)<br>Invoking SBA<br>SBA Parameters<br>HSIMSBA<br>HSIMSBANTL<br>HSIMSBAPARAM<br>HSIMSBAMSGLEVEL<br>HSIMSBAMSGLIMIT                              | 12<br>12<br>17<br>18<br>18<br>19<br>19<br>22<br>22       |

\_\_\_\_\_

|    | SP2DSPF Utility                                        | 24       |

|----|--------------------------------------------------------|----------|

|    | Generating a DSPF File From the Flat Extracted Netlist | 24       |

|    | Running SP2DSPF                                        | 24       |

|    | SP2DSPF Utility Parameters                             | 25       |

|    | -pre                                                   | 25       |

|    | -fpre                                                  | 25       |

|    | -pretop                                                | 25       |

|    | -post                                                  | 25       |

|    | -fpost                                                 | 25       |

|    | -posttop                                               | 26       |

|    | -an                                                    | 26       |

|    | -anan                                                  | 26<br>27 |

|    | -out                                                   | 27<br>27 |

|    | -dpf<br>-outdpf                                        | 27       |

|    | -dspf                                                  | 28       |

|    | -outdspf                                               | 28       |

|    | -pinports                                              | 28       |

|    | - ms                                                   | 28       |

|    | -mm                                                    | 29       |

|    | -opt outnf                                             | 29       |

|    | -opt outprefc                                          | 30       |

|    | -opt outhierc                                          | 30       |

|    | -opt outsubc                                           | 30       |

|    | -opt serial                                            | 30       |

|    | -opt capnet                                            | 30       |

|    | -opt dupcc                                             | 31       |

|    | -opt rpref                                             | 31       |

|    | -opt ccpref, -opt gcpref                               | 31<br>32 |

|    | -opt voi                                               | 32       |

|    |                                                        |          |

|    | References.                                            | 33       |

|    |                                                        |          |

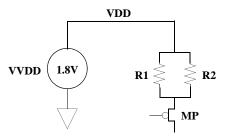

| 3. | Power Net Reliability Analysis (PWRA)                  | 35       |

|    | Power Net Reduction                                    | 36       |

|    | Specifics of Power Net Back-Annotation                 | 36       |

|    | HSIMPOSTL                                              | 36       |

|    |                                                        | 36       |

|    |                                                        | 37       |

|    |                                                        | 39       |

|    |                                                        | 39       |

|    | HSIMTMPDIR                                             | 40       |

| HSIMSPFTLV.40Package Modeling41HSIMSPFNETIPIN41HSIMSPFMERGEPIN43HSIMSPFNETPPIN44                                                |

|---------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                 |

|                                                                                                                                 |

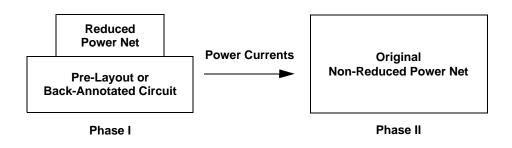

| Phase I                                                                                                                         |

| Phase II                                                                                                                        |

| Phase I Control Parameters. 45                                                                                                  |

| HSIMSPF                                                                                                                         |

| 45 HSIMSPFPWNET                                                                                                                 |

| HSIMRAP2AUTO                                                                                                                    |

| HSIMRAKEEPSERIESR                                                                                                               |

| HSIMRATAU                                                                                                                       |

| 46 HSIMRATCL                                                                                                                    |

| HSIMRARMIN                                                                                                                      |

| HSIMSPFPWRMIN 47                                                                                                                |

| HSIMRAP2AUTO                                                                                                                    |

| HSIMRATAU                                                                                                                       |

| HSIMRATCL                                                                                                                       |

| HSIMOUTPUT                                                                                                                      |

| HSIMRAIRMIN                                                                                                                     |

| Phase II Control Parameters   49                                                                                                |

| Defining Net Pins by Specifying X/Y Coordinates                                                                                 |

| Output Files                                                                                                                    |

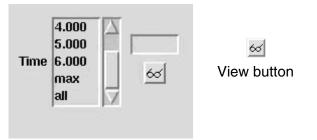

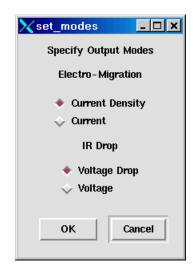

| Violation Map Visualization                                                                                                     |

| Generating a Violation Map 58                                                                                                   |

| Generating Multiple GDSII Files with One Command                                                                                |

| Generating GDSII for All Analyses                                                                                               |

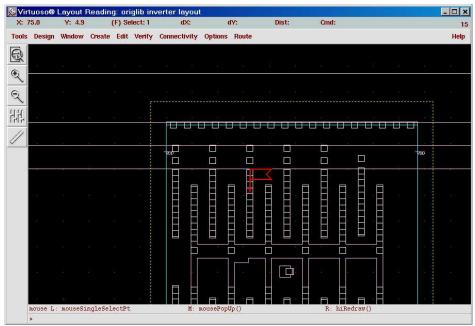

| Generating a Violation Map over the Original Layout                                                                             |

| Displaying a Map Legend                                                                                                         |

| User-Specified Layer Numbers                                                                                                    |

|                                                                                                                                 |

| , .                                                                                                                             |

| Names Inserted into Geometry       60         Concerting Lowert Formation       60                                              |

| Generating Layout Formats                                                                                                       |

| Automatically Generating Violation Maps         60                                                                              |

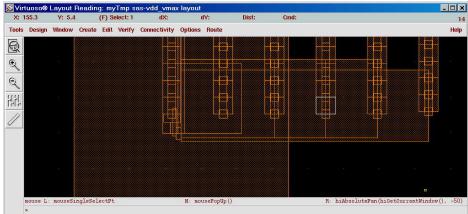

| Loading GDSII Files into the Cadence Virtuoso Layout Editor       61         Loading the IR Drop/EM Violation Map Only       61 |

| Loading a Violation Map Over the Original Layout. | 62 |

|---------------------------------------------------|----|

| .ratcl File Commands for Phase II Control         | 62 |

| ra val                                            | 62 |

| raout                                             | 63 |

| ralayout                                          | 63 |

| coordunit                                         | 64 |

| redv                                              | 64 |

| rediw                                             | 66 |

| redimaxw, redirmsw, rediabsw, rediavgw            | 68 |

| redia                                             | 68 |

| redimaxa, redirmsa, rediabsa, rediavga            | 68 |

| redj                                              | 69 |

| emthreshproc, emldlayers                          | 69 |

| emlmaxiv, emlmaxim                                | 75 |

| jjmaxlog                                          | 76 |

| ragds                                             | 76 |

| raformat                                          | 76 |

| ralayers.                                         | 76 |

| printi                                            | 70 |

| printv                                            | 77 |

| •                                                 | 77 |

| printvmode                                        | 78 |

| printipad                                         | 78 |

| alterpad                                          | 78 |

| gdslabels                                         | -  |

|                                                   | 79 |

| skiplayers                                        | 79 |

| outfiltres                                        | 80 |

| gdsmapvmax                                        | 80 |

| gdsmapi                                           | 81 |

| gdsoutmode                                        | 81 |

| gdsmag                                            | 82 |

| tstart                                            | 83 |

| tstop                                             | 83 |

| swin                                              | 83 |

| twin                                              | 86 |

| tau                                               | 86 |

| layerh                                            | 86 |

| layerea                                           | 87 |

| layermap                                          | 87 |

| rvemapvmax                                        | 87 |

| rvemapi                                           | 87 |

| asciimapvmax                                      | 88 |

| asciimapi                                         | 88 |

| asciicols                                         | 89 |

| asciicolsort                                      | 90 |

|                                    | 91                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gdstiming                          | 92                                                                                                                                                                                                                                                                                                                                                                                      |

| gdsdefrw                           | 93                                                                                                                                                                                                                                                                                                                                                                                      |

| gdsdatatype                        | 93                                                                                                                                                                                                                                                                                                                                                                                      |

| gdsfilechsymb                      | 93                                                                                                                                                                                                                                                                                                                                                                                      |

| deflayer                           | 94                                                                                                                                                                                                                                                                                                                                                                                      |

| rarve                              | 94                                                                                                                                                                                                                                                                                                                                                                                      |

|                                    | 94                                                                                                                                                                                                                                                                                                                                                                                      |

|                                    | 95                                                                                                                                                                                                                                                                                                                                                                                      |

|                                    | 96                                                                                                                                                                                                                                                                                                                                                                                      |

|                                    | 96                                                                                                                                                                                                                                                                                                                                                                                      |

| avgviagrp                          | 97                                                                                                                                                                                                                                                                                                                                                                                      |

| Internal Power Nets                | 98                                                                                                                                                                                                                                                                                                                                                                                      |

| References.                        | 100                                                                                                                                                                                                                                                                                                                                                                                     |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                         |

|                                    | 101                                                                                                                                                                                                                                                                                                                                                                                     |

| Power Net Resistance Calculator    | 101                                                                                                                                                                                                                                                                                                                                                                                     |

| hsim -r                            | 101                                                                                                                                                                                                                                                                                                                                                                                     |

| hsim -rout                         | 102                                                                                                                                                                                                                                                                                                                                                                                     |

| routcols                           | 102                                                                                                                                                                                                                                                                                                                                                                                     |

| Net Resistance Calculator Commands | 103                                                                                                                                                                                                                                                                                                                                                                                     |

| file                               |                                                                                                                                                                                                                                                                                                                                                                                         |

|                                    | 103                                                                                                                                                                                                                                                                                                                                                                                     |

| net                                | 103<br>103                                                                                                                                                                                                                                                                                                                                                                              |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                         |

| net                                | 103                                                                                                                                                                                                                                                                                                                                                                                     |

| net                                | 103<br>104                                                                                                                                                                                                                                                                                                                                                                              |

| net                                | 103<br>104<br>104<br>104                                                                                                                                                                                                                                                                                                                                                                |

| net                                | 103<br>104<br>104<br>104<br>104                                                                                                                                                                                                                                                                                                                                                         |

| net                                | 103<br>104<br>104<br>104<br>104<br>105                                                                                                                                                                                                                                                                                                                                                  |

| net                                | 103<br>104<br>104<br>104<br>104<br>105<br>105                                                                                                                                                                                                                                                                                                                                           |

| netaddnetpin                       | 103<br>104<br>104<br>104<br>104<br>105<br>105                                                                                                                                                                                                                                                                                                                                           |

| net                                | 103<br>104<br>104<br>104<br>104<br>105<br>105<br>106                                                                                                                                                                                                                                                                                                                                    |

| netaddnetpin                       | 103<br>104<br>104<br>104<br>105<br>105<br>106<br>106                                                                                                                                                                                                                                                                                                                                    |

| net                                | 103<br>104<br>104<br>104<br>104<br>105<br>105<br>106                                                                                                                                                                                                                                                                                                                                    |

| netaddnetpin                       | 103<br>104<br>104<br>104<br>105<br>105<br>106<br>106                                                                                                                                                                                                                                                                                                                                    |

| net                                | 103<br>104<br>104<br>104<br>105<br>105<br>106<br>106<br>106                                                                                                                                                                                                                                                                                                                             |

| net                                | 103<br>104<br>104<br>104<br>105<br>105<br>106<br>106<br>106<br>106<br>107                                                                                                                                                                                                                                                                                                               |

| net                                | 103<br>104<br>104<br>104<br>105<br>105<br>106<br>106<br>106<br>106<br>107                                                                                                                                                                                                                                                                                                               |

| net                                | 103<br>104<br>104<br>104<br>105<br>105<br>106<br>106<br>106<br>106<br>107<br>107                                                                                                                                                                                                                                                                                                        |

|                                    | gdsfilechsymb.         deflayer.         rarve.         rarve.         raviewer         rediac         redirmst         redtrms.         avgviagrp         Internal Power Nets         References.         Static Power Net Resistance (SPRES).         Power Net Resistance Calculator         hsim -r         hsim -rout         routcols.         Net Resistance Calculator Commands |

-

|    | Method 2: Command Line Execution                    | 108<br>108 |

|----|-----------------------------------------------------|------------|

|    | Report File Generation Options                      | 108        |

|    | Power Net IR Drop and EM Analysis Flow              | 110        |

|    | Phase I                                             | 110        |

|    | Phase II                                            | 110        |

|    | Phase I Control Parameters.                         | 111        |

|    | HSIMSPF                                             | 111        |

|    | HSIMSPFPWNET                                        | 111        |

|    | HSIMPWRA                                            | 111        |

|    | HSIMRAP2AUTO                                        | 111        |

|    | HSIMRATAU                                           | 112        |

|    | HSIMRATCL                                           | 112        |

|    | HSIMRARMIN                                          | 113        |

|    | HSIMSPFPWRMIN                                       | 113        |

|    | HSIMRAP2AUTO                                        | 113        |

|    | HSIMRATAU                                           | 113        |

|    | HSIMRATCL                                           | 114        |

|    | HSIMOUTPUT                                          | 114        |

|    | HSIMRAIRMIN                                         | 114        |

|    | Phase II Control Parameters                         | 115        |

|    | Defining Net Pins by Specifiying X/Y Coordinates    | 116        |

|    |                                                     |            |

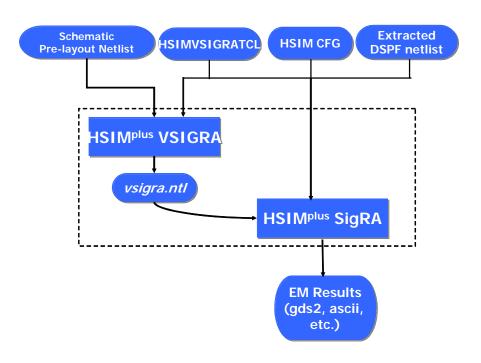

| 5. | Signal Net Reliability Analysis (SIGRA)             | 119        |

|    | Overview                                            | 119        |

|    | Dhase I Control Devenators                          | 100        |

|    | Phase I Control Parameters.                         | 120        |

|    | HSIMSIGRA                                           | 120        |

|    | HSIMRASIGCONLY                                      | 120        |

|    | HSIMRANET                                           | 120        |

|    | HSIMSKIPRANET                                       | 121        |

|    | Phase II Controlractl File Commands                 | 121        |

|    | iavmin val                                          | 121        |

|    | nnetmax num                                         | 122        |

|    |                                                     |            |

|    | selectsignets                                       | 122        |

|    | Vectorless Signal Net Reliability Analysis (VSIGRA) | 122        |

|    | VSIGRA Flow                                         | 123        |

|    | HSIMVSIGRA                                          | 125        |

|    | HSIMVSIGRATCL                                       | 125        |

|    |                                                     |            |

|    | VSIGRA CFG TCL File                                 | 125        |

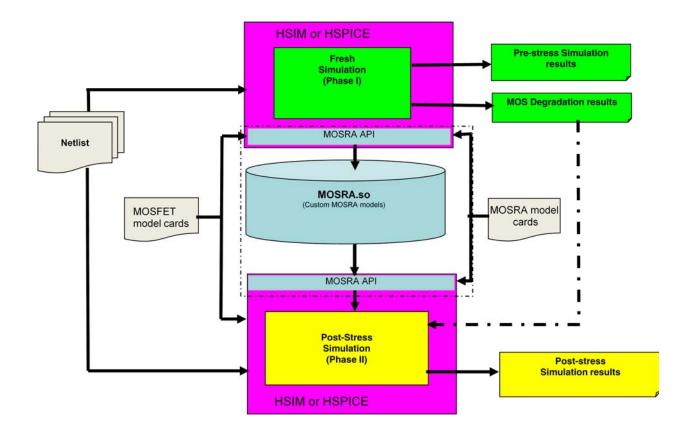

| 6. | MOSFET Reliability Analysis (MOSRA)                                                                                                                                                                                       | 127                                                                |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|    | Overview of MOSFET Reliability Analysis (MOSRA).                                                                                                                                                                          | 127                                                                |

|    | Fresh Simulation                                                                                                                                                                                                          | 128                                                                |

|    | Post-Stress Simulation.                                                                                                                                                                                                   | 128                                                                |

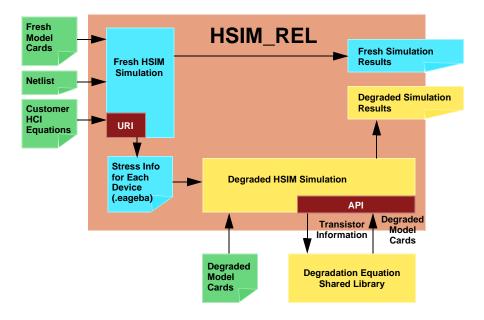

|    | User Reliability Interface (URI)                                                                                                                                                                                          | 129                                                                |

|    | Simulation Control Parameters<br>HSIMAGINGINST<br>HSIMAGINGSTART, HSIMAGINGSTOP<br>HSIMHCIEAGEREFINST.<br>HSIMHCIEAGETHRESHOLD<br>HSIMHCIEAGESAMPLING<br>HSIMMOSRASIM.<br>HSIMRELMODE<br>HSIMRELTOTALTIME.<br>HSIMURILIB. | 129<br>129<br>129<br>130<br>130<br>130<br>130<br>131<br>131<br>131 |

|    | HCIappendmodel<br>Post-Stress Simulation Models                                                                                                                                                                           | 131<br>132<br>133                                                  |

|    | Output Files<br>Fresh Simulation<br>Post-Stress Simulation                                                                                                                                                                | 136<br>136<br>137                                                  |

|    | API Access                                                                                                                                                                                                                | 137<br>137<br>137                                                  |

|    | MOSRA Print Commands                                                                                                                                                                                                      | 138                                                                |

|    | MOSRA Examples       Fresh Simulation Netlist Example         Fresh Simulation Outputs.       Post-Stress Simulation Netlist Example         Associated Transistors Using the Degraded Model       Post-Stress            | 138<br>138<br>139<br>140<br>142                                    |

|    | Overview of the Unified MOSRA Solution                                                                                                                                                                                    | 142<br>144<br>144                                                  |

|    | Output Files for Fresh and Post-Stress Simulations         API Access                                                                                  | 144<br>145                      |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|    | Running the MOSRA Flow.       Running a MOSRA Example with Built-In Equations.         Running a MOSRA API Example.       Running a MOSRA API Example. | 145<br>145<br>147               |

|    | Correlating the MOSRA Output Files with HSPICE                                                                                                         | 147<br>147<br>148               |

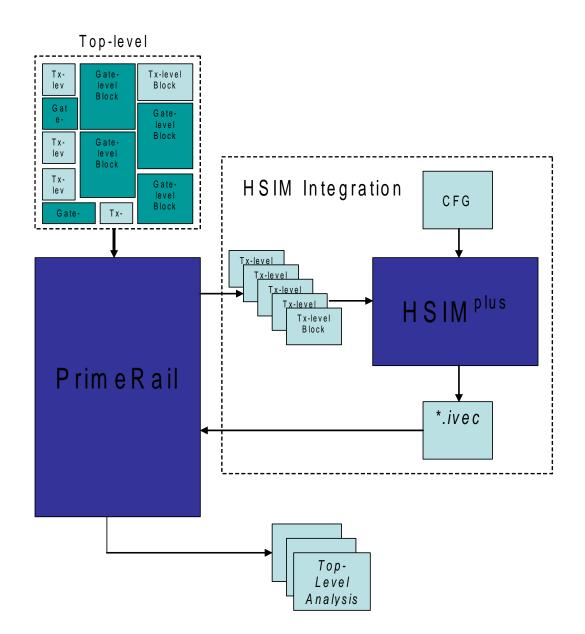

| 7. | HSIM <sup>plus</sup> -PrimeRail Interface                                                                                                              | 149                             |

|    | HSIM <sup>plus</sup> PrimeRail Flow<br>HSIM Simulation<br>HSIMPRIMERAIL<br>HSIMPRIMERAILTCL                                                            | 149<br>150<br>153<br>153        |

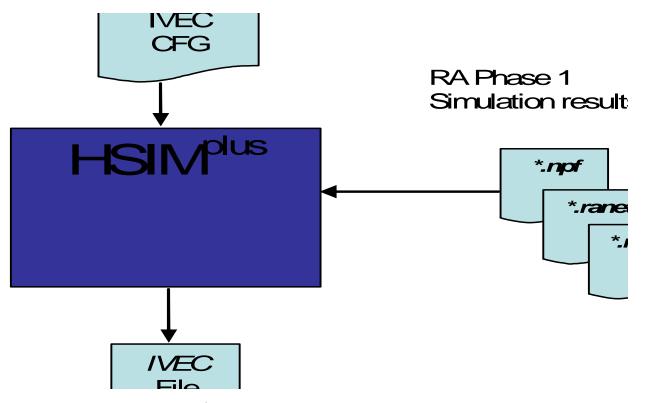

|    | Combining HSIM <sup>plus</sup> -PrimeRail Interface with PWRA Options<br>HSIM Re-use Simulation Results Option (Phase I RA Results Re-use).            | 153<br>155                      |

|    | IVEC CFG TCL File Syntax                                                                                                                               | 156<br>158                      |

| 8. | CircuitCheck                                                                                                                                           | 159                             |

|    | Overview of CircuitCheck (CCK) Option<br>CircuitCheck Tutorial<br>Conventions                                                                          | 159<br>160<br>160               |

|    | CircuitCheck Command Usage                                                                                                                             | 160<br>165                      |

|    | Passing Parameters Into CircuitCheck Commands.         CircuitCheck.cck         Include Statements                                                     | 168<br>169<br>170               |

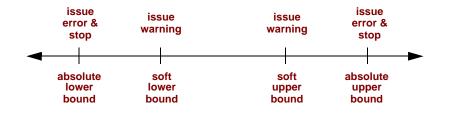

|    | Parametric Checks.<br>Check Electrical Parameters<br>cckParam<br>Capacitor Values<br>MOSFET Width                                                      | 170<br>170<br>170<br>172<br>172 |

| MOSFET Length                                               | 173 |

|-------------------------------------------------------------|-----|

| MOSFET Drain/Source Area and Drain/Source Perimeter         | 173 |

| MOSFET Gate Oxide Thickness                                 | 174 |

| Diode Width, Length, and Area                               | 174 |

| Simulation Run Temperature                                  | 175 |

| Model                                                       | 175 |

| Limiting the Number of Violations Reported                  | 178 |

| M-factor                                                    | 178 |

| Post-Layout RC Checking                                     | 179 |

| cckParasiticRC                                              | 179 |

| Design and Electrical Rules Check                           | 181 |

| Static Device Voltage Analysis.                             | 181 |

| Device Voltage Analysis for Transistors                     | 182 |

| cckMosV                                                     | 182 |

| Device Voltage Analysis for Capacitor, Resistor and Diode   | 190 |

| cckCapV                                                     | 190 |

| cckDioV                                                     | 191 |

| cckResV                                                     | 191 |

| Subcircuit-Based Voltage Analysis Using the Static Approach | 198 |

| cckSubV                                                     | 198 |

| Diode Forward Bias Analysis                                 | 203 |

| cckDiode                                                    | 203 |

| Element Current Analysis.                                   | 206 |

| cckEleml                                                    | 206 |

| Instance and Subcircuit Reference Check                     | 207 |

| cckMatchSub                                                 | 207 |

| Excessive Current Path Detection                            | 208 |

| cckExiPath                                                  | 208 |

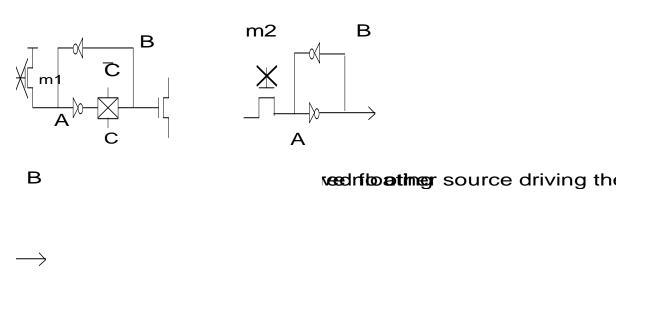

| Floating Gates and Current Sources Analysis                 | 209 |

| cckFloatGateIsrc                                            | 209 |

| Check NMOS Bulk Connections                                 | 211 |

| cckNmosB_gt_DS                                              | 211 |

| Example                                                     | 216 |

| Find Potentially Conducting NMOS Devices                    | 216 |

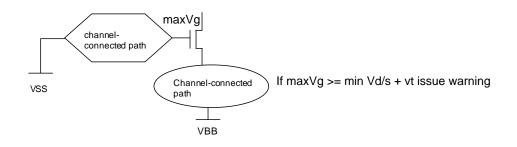

| cckNmosG_gt_DS                                              | 216 |

| Check NMOS Node to VDD Connection                           | 222 |

| cckNmosNodeToVdd                                            | 222 |

| Check Node Voltage                                          | 224 |

| cckNodeVoltage                                              | 224 |

| Check Paths to Voltage Sources                              | 226 |

| cckPathToVsrc                                               | 226 |

| Check PMOS Bulk Connections                                 | 230 |

|                                                             |     |

| cckPmosB_lt_DS                                               | 230        |

|--------------------------------------------------------------|------------|

| Example                                                      | 235        |

| Find Potentially Conducting PMOS DevicescckPmosG_It_DS       | 236<br>236 |

| Check PMOS Node To GND Connection                            | 244        |

| cckPmosNodeToGnd                                             | 244        |

| Safe Operating Area Check                                    | 245        |

| cckSOA                                                       | 245        |

| Subcircuit-Based Voltage Analysis Using the Dynamic Approach | 249        |

| cckDynSubV                                                   | 249        |

| Substrate Forward Bias Check                                 | 253        |

|                                                              | 253<br>253 |

|                                                              |            |

| Unprotected Antenna Node Check                               | 256        |

| cckAntGate                                                   | 256        |

| Static Voltage Propagation Sharing                           | 257        |

| Propagation Parameters                                       | 257        |

| Propagation Sharing.                                         | 258        |

| Example                                                      | 258        |

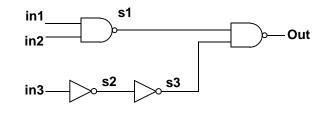

| Digital Logic and Memory Diagnostics.                        | 260        |

| Flash Memory Check                                           | 260        |

| cckFlashcore                                                 | 260        |

| Find Un-initialized Latch                                    | 262        |

| cckLatchUnInit                                               | 262        |

| cckLatchInElem                                               | 263        |

| cckLatchSkipElem                                             | 264        |

| Check Stack-up Transistors                                   | 265        |

| cckMaxStackUpNmos                                            | 265        |

| cckMaxStackUpPmos                                            | 265        |

| Check and Classify the Stuck Nodes                           | 266        |

| cckMaxStuckAt.                                               | 266        |

| cckToggleCount                                               | 267        |

| cckConnReport                                                | 268        |

| Interactive Circuit Debugging Command for Tracking Circuit   | 269        |

| Finding a Node's First State Change After a Specified Time   | 270        |

| ntrig                                                        | 270        |

| intrig                                                       | 274        |

| Timing Checks                                                | 277        |

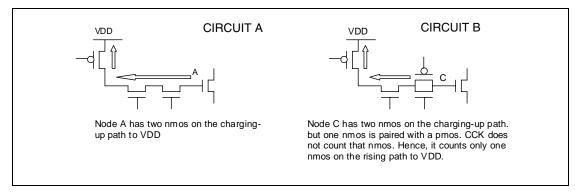

| Check Number of n-MOSFET in Charging Path to VDD             | 278        |

| cckMaxNmosToVdd                                              | 278        |

| Check Number of p-MOSFET in Discharging Path to GND          | 279        |

| cckMaxPmosToGnd.                                             | 279        |

|                                                              |            |

| cckMaxStackUpNmos                                         | 280        |

|-----------------------------------------------------------|------------|

| cckMaxStackUpPmos                                         | 280        |

| Checking Path Delay Between Two Nodes                     | 280        |

| cckMeasPathDelay                                          | 280        |

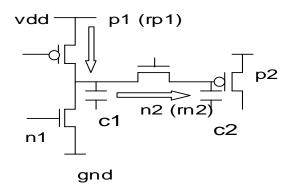

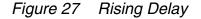

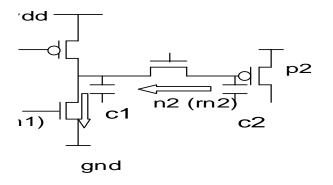

| Estimating the Rise and Fall Delay at a Node              | 282        |

|                                                           | 282        |

|                                                           | 283        |

| Static RC Delay Analysis – Estimate Slew RatecckRCDlyPath | 284<br>284 |

| Delay Path Sub-Commands.                                  | 284        |

| cckDlyAtNode                                              | 285        |

| cckDlySkipElem                                            | 285        |

| cckDlySkipNode                                            | 285        |

| cckLimitRisePmosFallNmos                                  | 286        |

| cckRCFallDelay                                            | 286        |

| cckRCRiseDelay                                            | 286        |

|                                                           | 287        |

| Computing the Resistance of MOSFET                        | 288<br>289 |

| Explanation of this Rising Path Report.                   | 209<br>291 |

| Explanation of this Falling Path Report:                  | 293        |

| Dynamic Device Voltage Check.                             | 294        |

| tcheck mosv                                               | 294        |

|                                                           | 294        |

| tag_name                                                  |            |

| mosv                                                      | 296        |

| subckt                                                    | 297        |

| mos                                                       | 298        |

| model                                                     | 298        |

| report                                                    | 300        |

| time                                                      | 300        |

| parallel                                                  | 300        |

| separate_file                                             | 301        |

| Output Sorting                                            | 301        |

| start/stop                                                | 302        |

| step                                                      | 302        |

| tcheck bjtv                                               | 302        |

| tcheck diodev                                             | 304        |

| tcheck capv                                               | 305        |

| Post-Process Device Voltage Check                         | 305        |

| Method 1                                                  | 306        |

| Method 2                                                  | 306        |

| Signal Integrity Checks                                    | 307 |

|------------------------------------------------------------|-----|

| Dynamic Crosstalk Analysis                                 | 307 |

| cckDXtalk                                                  | 308 |

| Signal Edge Characteristics                                | 310 |

| Thresholds                                                 | 310 |

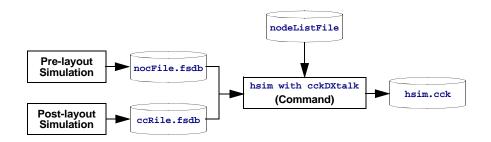

| Usage Flow Methods                                         | 311 |

| Method 1                                                   | 311 |

| Method 2                                                   | 312 |

| cckParasiticRC                                             | 314 |

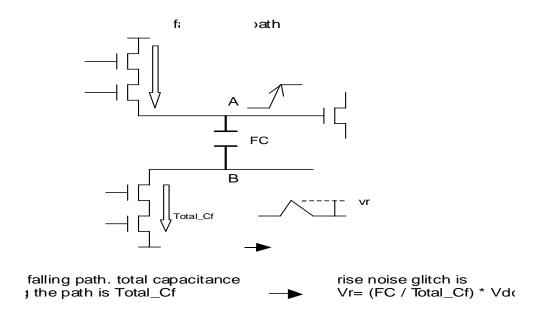

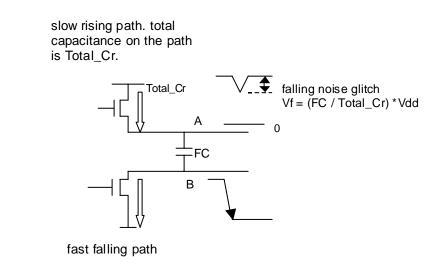

| Static Crosstalk Noise Analysis: Estimating Noise Glitches | 314 |

| Running Crosstalk Glitch Analysis                          | 315 |

| hsim.cckxtk Output Sample                                  | 319 |

| hsim.cckvr Output Sample                                   | 320 |

| hsim.cckvf Output Sample                                   | 320 |

| cckxtk Output Sample                                       | 322 |

| hsim.cckvr Output Sample                                   | 322 |

| hsim.cckvf Output Sample                                   | 323 |

|                                                            |     |

| Leakage Current Detection                                  | 323 |

| Detect Leakage Paths Between Voltage Supply Nodes          | 324 |

| cckMaxStaticLeak                                           | 324 |

| Leakage Current Detection in Non-Conducting Transistors.   | 325 |

|                                                            | 325 |

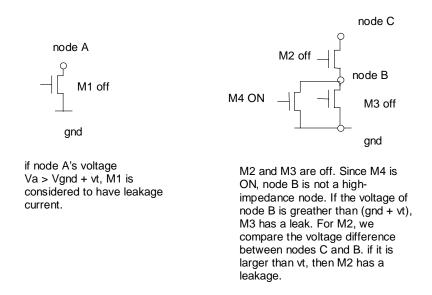

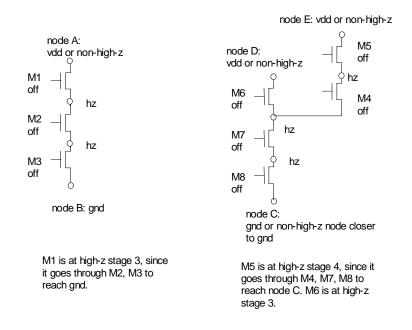

| Leakage Current in OFF Transistor                          | 326 |

| Leakage Current Ratio                                      | 328 |

|                                                            | 330 |

| Power-Down Floating-Gate Checking                          | 332 |

| cckAnalogPDown                                             | 332 |

| cckAnalogPDownIth                                          | 332 |

| cckElemI                                                   | 333 |

| cckExiPath                                                 | 334 |

| Static Analysis                                            | 334 |

| Static 0 and Static 1 Notes.                               | 334 |

| Static High Impedance Node                                 | 335 |

| cckStaticHZNode                                            | 335 |

| Static DC Path                                             | 337 |

| cckStaticDCPath                                            | 337 |

| CircuitCheck Utilities                                     | 338 |

| Basic Checking                                             | 338 |

| cckBasic                                                   | 338 |

| Comparing DC Results Between HSIM and Other Simulators     | 339 |

| cckCompareOp                      | 339 |

|-----------------------------------|-----|

| Find Subcircuit Instances         | 342 |

| cckMatchSub                       | 342 |

| Pattern Matching Capability       | 343 |

| cckPatternMatch                   | 343 |

| cckPatternConstraint              | 345 |

| cckSetMosDir                      | 346 |

| Setting Transistor Directions     | 347 |

| cckTgPair                         | 347 |

| Global Parameter Settings         | 349 |

| CircuitCheck Tutorial             | 351 |

| Invoking CircuitCheck             | 351 |

| Test Case                         | 352 |

| Test Case Example for tcheck mosv | 355 |

| Run HSIM                          | 355 |

|                                   |     |

| 9. | HSIM-ADMS Integration.                                                                                                                                                                      | 357                                    |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|    | Introduction to HSIM-ADMS                                                                                                                                                                   | 357<br>357                             |

|    | HSIM-ADMSTool Setup<br>Licensing<br>Mentor ADMS License<br>Synopsys HSIM License<br>Installing and Configuring ADMS                                                                         | 358<br>358<br>358<br>358<br>358<br>358 |

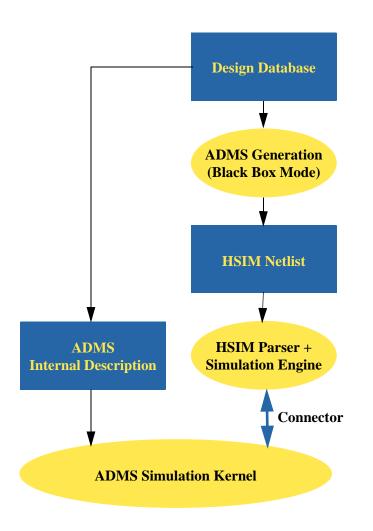

|    | HSIM-ADMS High-level Architecture and Data Flow                                                                                                                                             | 359<br>360                             |

|    | HSIM-ADMS Examples                                                                                                                                                                          | 362                                    |

|    | HSIM-ADMS Configuration Commands                                                                                                                                                            | 366<br>366<br>367<br>367<br>367        |

|    | HSIM-ADMS Control Options<br>Passing HSIM Options in HSIM-ADMS<br>Passing HSIM Options in the ADMS Netlist File<br>Passing HSIM Options on the ADMS Command Line<br>HSIM-ADMS DC Iterations | 368<br>368<br>369<br>369<br>369        |

-

|     | HSIM-ADMS Boundary Elements                                                        | 369<br>370<br>370 |

|-----|------------------------------------------------------------------------------------|-------------------|

|     |                                                                                    |                   |

|     | HSIM-ADMS Outputs.                                                                 | 371               |

|     |                                                                                    | 371               |

|     | Waveform Outputs                                                                   | 371               |

|     | Black Box Mode Limitations[1]                                                      | 371               |

|     | References                                                                         | 373               |

| 10. | HSIM-Virtuoso Analog Design Environment Interface                                  | 375               |

|     | HSIM Virtuoso Analog Design Environment Interface Package Options and Pla Support. | tform.<br>375     |

|     | All-In-One Package (AAIM)                                                          | 376               |

|     | AAIM Installation & Setup                                                          | 376               |

|     | AAIM Uninstallation                                                                | 378               |

|     | Native Netlist Integration (AANNI)                                                 | 378               |

|     | Native Netlist Integration Installation & Setup                                    | 378               |

|     | Native Netlist Integration Features.                                               | 378               |

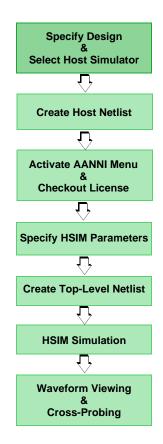

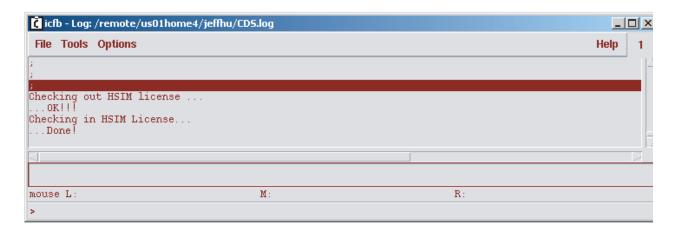

|     | Basic Native Netlist Integration Flow                                              | 379               |

|     | Porting the Existing Design                                                        | 380               |

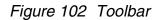

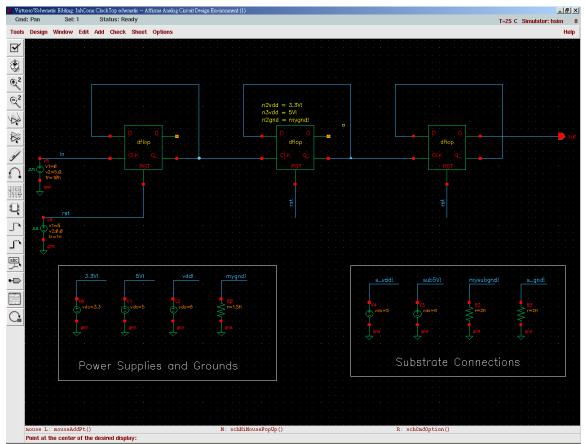

|     | Native Netlist Integration Window and Pull-Down Menus                              | 380               |

|     | Environment Setup                                                                  | 383               |

|     | Basic Setup                                                                        | 383               |

|     | Advanced Setup                                                                     | 383               |

|     | Setup Parameters                                                                   | 386               |

|     | Netlisting                                                                         | 387               |

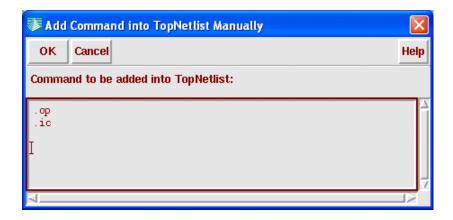

|     | Create Top Netlist                                                                 | 387<br>388        |

|     | Edit Top Netlist                                                                   | 389               |

|     | View Host Netlist                                                                  | 389               |

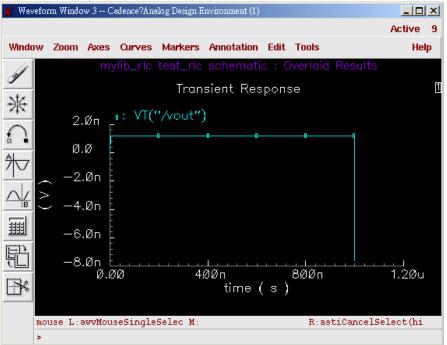

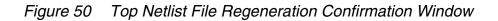

|     | Run HSIM.                                                                          | 389               |

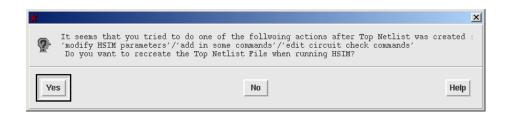

|     | Regenerate the Netlist and Run HSIM                                                | 391               |

|     | Toggle between Spectre and HSIM Simulation Database for Waveform Pr<br>391         | obing             |

|     | Toggle Flow I:                                                                     | 392               |

|     | Toggle Flow II:                                                                    | 393               |

|     | CircuitCheck in the HSIM-Virtuoso Interface Environment                            | 394               |

|     | View Log File                                                                      | 394               |

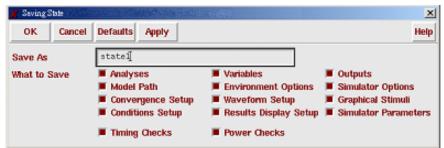

|     | View Output ASCII Files<br>Save/Load States<br>Check in Synopsys License<br>Cadence Cross-probing                                                                                               | 395<br>395<br>397<br>398        |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

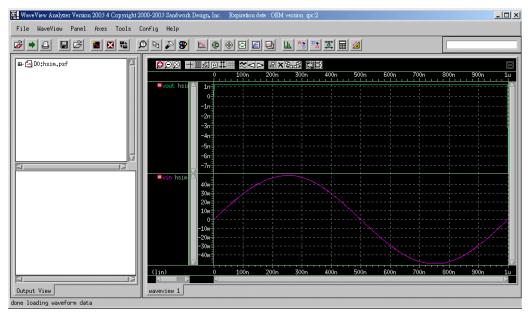

|     | WaveView Analyzer Cross-probing                                                                                                                                                                 | 402                             |

|     | CoSim (AACoSim) Integration<br>UNIX Setup<br>CoSim Installation<br>Basic CoSim Flow                                                                                                             | 404<br>404<br>404<br>405        |

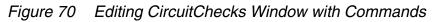

|     | HSIM-Virtuoso CircuitCheck Integration<br>Native Netlist CircuitCheck<br>Viewing Commands When Multiple Commands Are Applied<br>cckCommandFile, cckDeviceVFile<br>WaveView Analyzer Integration | 405<br>405<br>413<br>414<br>414 |

| 11. | Verilog/VHDL/HSIM Co-Simulation.                                                                                                                                                                | 417                             |

|     | Setting Up System Environment Variables for Co-Simulation                                                                                                                                       | 418                             |

|     | Co-Simulation with Verilog as the Top Instance                                                                                                                                                  | 419<br>419<br>419               |

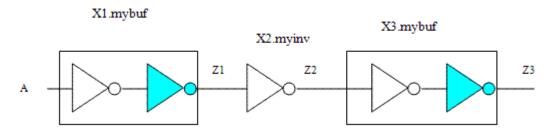

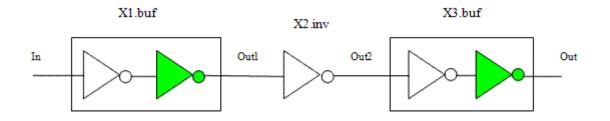

|     | Instance Based Instantiation with Verilog Configuration                                                                                                                                         | 424                             |

|     | Co-Simulation with VHDL as the Top Instance                                                                                                                                                     | 426                             |

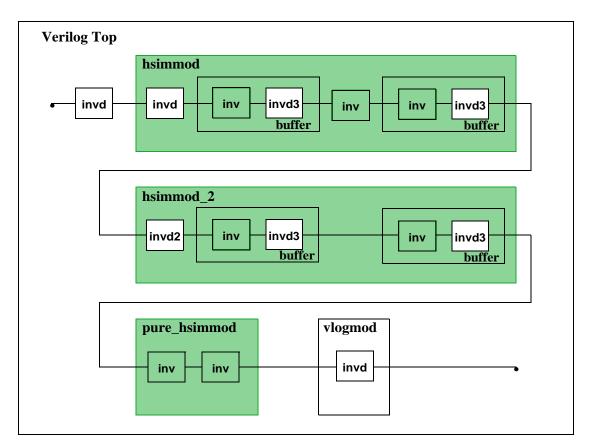

|     | Co-Simulation with SPICE as the Top Instance.                                                                                                                                                   | 432                             |

|     | Spectre/Verilog Co-Simulation Running Under the Virtuoso Analog Design<br>Environment                                                                                                           | 435                             |

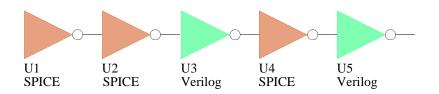

|     | Donut Partitioning with Verilog as the Top Instance (V-S-V) Using Verilog-on-Top Partitioning                                                                                                   | 436<br>436<br>439<br>439<br>440 |

|     | Donut Partitioning with SPICE as the Top Instance (S-V-S)         Using SPICE-on-Top Partitioning.         First Run Example         Second Run Example         Verilog and SPICE Files.        | 443<br>443<br>445<br>445<br>446 |

|     | Save-Restart in Co-Simulation.                                                                                                                                                                  | 447                             |

| Appending a Waveform in Co-Simulation  | 448 |

|----------------------------------------|-----|

| Configuration File Commands            | 448 |

| analog_cell                            | 448 |

| auto_vsrc_warning                      | 449 |

| correct_netlist.                       | 450 |

| define_print_variable                  | 450 |

| define_strength                        | 451 |

| digital_cell                           | 451 |

| digital_cell_inst                      | 452 |

| dump_interface                         | 452 |

| dump_port_prop                         | 453 |

| dump_setting                           | 453 |

| keep_iface_file                        | 453 |

| map_subckt_name                        | 454 |

| map_unfound_port                       | 454 |

| report_logic_delay                     | 454 |

| report_port_resistance                 | 455 |

| set_args                               | 455 |

| set_intr_mode                          | 456 |

| set_fall_step                          | 456 |

| set_port_prop                          | 456 |

| set_port_prop_warning                  | 460 |

| set_print_progress                     | 460 |

| set_rise_step                          | 460 |

| set_slope_step                         | 461 |

| set_verbose                            | 461 |

| set_verilog_supply1                    | 462 |

| set_verilog_supply0                    | 462 |

| verilog_file                           | 462 |

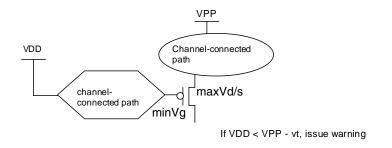

| Automatic Voltage Level Detection      | 463 |

| Voltage Setting Rules.                 | 463 |

| Rule 1                                 | 463 |

| Rule 2                                 | 463 |

| Rule 3                                 | 463 |

| Co-Simulation Interactive Mode         | 463 |

| List Interface Nodes                   | 465 |

| csli                                   | 465 |

| Print Global Interface History in Time | 466 |

| csh                                    | 466 |

| Print Interface Node Historycsnh, csinh                                     | 467<br>467  |

|-----------------------------------------------------------------------------|-------------|

| Set the Number of Entries Printed By csnh and csinh                         | 467<br>467  |

| csnph                                                                       | 467         |

| Set Watchpoint to Interface Node                                            | 468         |

| csnw, csinw                                                                 | 468         |

| Delete Watchpointcsdnw, csdinw                                              | 469<br>469  |

| Verilog System Tasks for Co-Simulation                                      | 469         |

| Co-Simulation Setup Guidelines                                              | 471         |

| Map Correct Port Voltages                                                   | 471         |

| Define Clear Port Direction                                                 | 471         |

| Set Input Ports As Voltage Sources If Possible                              | 471         |

| Define SPICE Netlist Bus Notation                                           | 471         |

| Handle Bi-Directional Ports                                                 | 472         |

| Partitioning Guidelines                                                     | 472         |

| Partition Boundary with Clear Digital Behavior                              | 472         |

| Avoid Partitioning at Timing Sensitive Signals                              | 472         |

| Avoid Reach-in Signals in Analog Partitions                                 | 472         |

| Avoid Partitioning at Bi-directional Signals Involved Strength Fighting and | Pass<br>473 |

| Switches                                                                    | 473         |

|                                                                             |             |

| Strength Table Setup Guidelines                                             | 473         |

| Co-simulation with VCS                                                      | 475         |

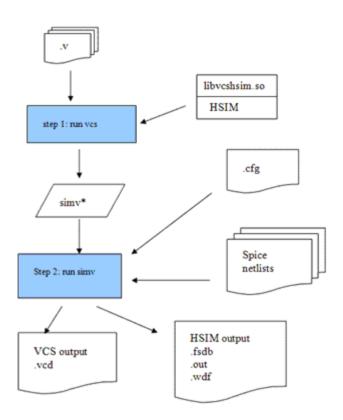

| HSIM-VCS Co-simulation Usage Flow.                                          | 476         |

| Setting up System Environment Variables for Co-simulation.                  | 477         |

| Running the Designs with Co-simulation                                      | 478         |

| Co-Simulation with Verilog as the Top Instance                              | 478<br>481  |

| Summary of Commands                                                         | 483         |

| Interactive Mode.                                                           | 483         |

|                                                                             | 484         |

| Platform Support for HSIM/VCS Co-Simulation                                 | 484         |

| Co-Simulation with ModelSim                                                 | 485         |

| ModelSim/HSIM Integration                                                   | 485         |

| Running ModelSim/HSIM Co-simulation with Stand-alone ModelSim               | 485         |

| Running ModelSim/HSIM Co-simulation Under the ADMS Environment              | 486         |