# ECE/CS 3700 Digital System Design

Lecture Slides for Chapter 2: Universal Logic

Priyank Kalla

Professor

Electrical & Computer Engineering

### Universal Logic

- A set of logical operators that can implement any arbitrary Boolean function

- {*AND*, *OR*, *NOT*}: collectively implement any Boolean function: universal logic

- ANDs and NOTs implement on-set minterms

- OR of on-set minterms = function

- Example: Majority function f = a'bc + ab'c + abc' + abc'

- Only NAND gates = universal logic [important, PLAs]

- Only NOR gates = universal logic [important, PLAs]

- Only MUXes = universal logic [important FPGAs]

- {*AND*, *XOR*} is also universal logic [important, to show off your mathematical reasoning prowess!]

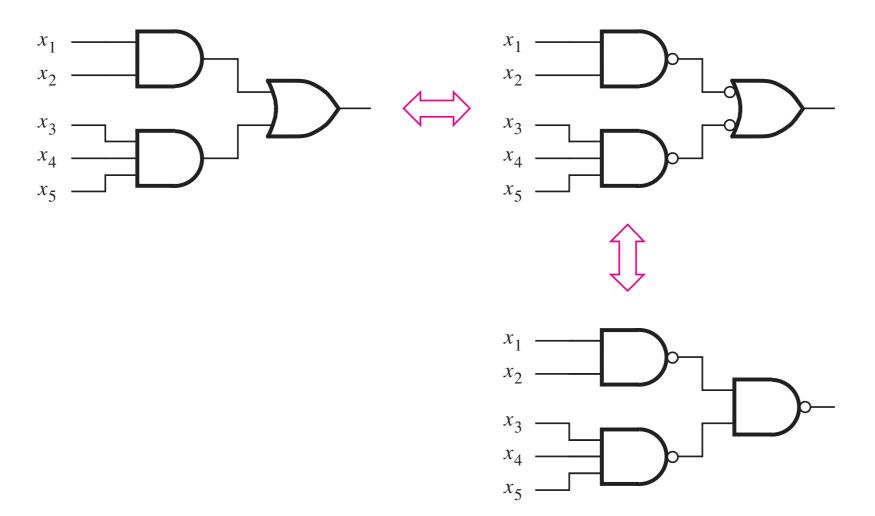

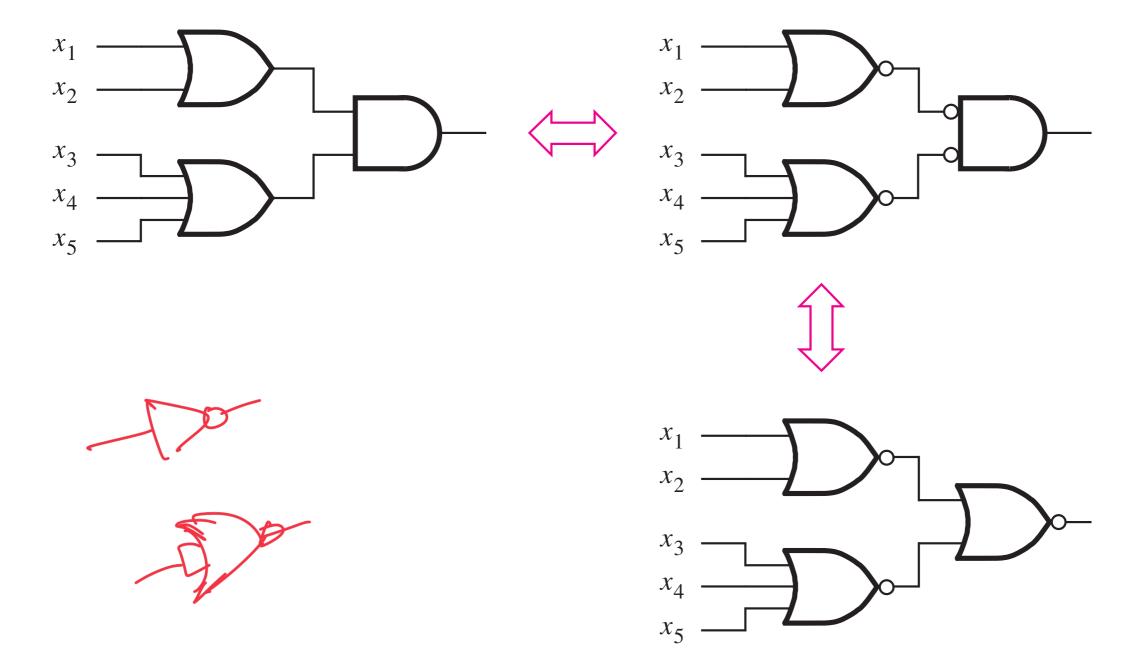

## Boolean functions implemented with only NAND gates

• Relies on DeMorgan's laws:  $\overline{x \cdot y} = \overline{x} + \overline{y}$

$\int_{a}^{b} \int_{a}^{b} \int_{a$

• f = ab + ac + bc

Do Do

# Maxterms and product of sum (POS) form

| Row<br>number                   | $x_1$                           | $x_2$                      | $x_3$                      | Minterm                                                                                                                                                                                                                                                       | Maxterm                                                                                                                                                                                                                       |

|---------------------------------|---------------------------------|----------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6 | 0<br>0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1 | $m_{0} = \bar{x}_{1}\bar{x}_{2}\bar{x}_{3}$ $m_{1} = \bar{x}_{1}\bar{x}_{2}x_{3}$ $m_{2} = \bar{x}_{1}x_{2}\bar{x}_{3}$ $m_{3} = \bar{x}_{1}x_{2}x_{3}$ $m_{4} = x_{1}\bar{x}_{2}\bar{x}_{3}$ $m_{5} = x_{1}\bar{x}_{2}x_{3}$ $m_{6} = x_{1}x_{2}\bar{x}_{3}$ | $M_0 = x_1 + x_2 + x_3$ $M_1 = x_1 + x_2 + \bar{x}_3$ $M_2 = x_1 + \bar{x}_2 + x_3$ $M_3 = x_1 + \bar{x}_2 + \bar{x}_3$ $M_4 = \bar{x}_1 + x_2 + x_3$ $M_5 = \bar{x}_1 + x_2 + \bar{x}_3$ $M_6 = \bar{x}_1 + \bar{x}_2 + x_3$ |

| 7                               | 1                               | 1                          | 1                          | $m_7 = x_1 x_2 x_3$                                                                                                                                                                                                                                           | $M_7 = \bar{x}_1 + \bar{x}_2 + \bar{x}_3$                                                                                                                                                                                     |

**Figure 2.22** Three-variable minterms and maxterms.

N=X

#### Maxterms and POS forms

| Row<br>number | $x_1$ | $x_2$ | $x_3$ | $f(x_1, x_2, x_3)$ |

|---------------|-------|-------|-------|--------------------|

| 0             | 0     | 0     | 0     | 0                  |

| 1             | 0     | 0     | 1     | 1                  |

| 2             | 0     | 1     | 0     | 0                  |

| 3             | 0     | 1     | 1     | 0                  |

| 4             | 1     | 0     | 0     | 1                  |

| 5             | 1     | 0     | 1     | 1                  |

| 6             | 1     | 1     | 0     | 1                  |

| 7             | 1     | 1     | 1     | 0                  |

$$\overline{f}(x_1, x_2, x_3) = m_0 + m_2 + m_3 + m_7$$

Then f can be expressed as

$$f = \overline{m_0 + m_2 + m_3 + m_7}$$

$$= \overline{m_0} \cdot \overline{m_2} \cdot \overline{m_3} \cdot \overline{m_7}$$

$$= M_0 \cdot M_2 \cdot M_3 \cdot M_7$$

$$= (x_1 + x_2 + x_3)(x_1 + \overline{x_2} + x_3)(x_1 + \overline{x_2} + \overline{x_3})(\overline{x_1} + \overline{x_2} + \overline{x_3})$$

$$f(x_1, x_2, x_3) = \Pi(M_0, M_2, M_3, M_7)$$

$$f = \mathcal{L}(m_1, m_4, m_5, m_6)$$

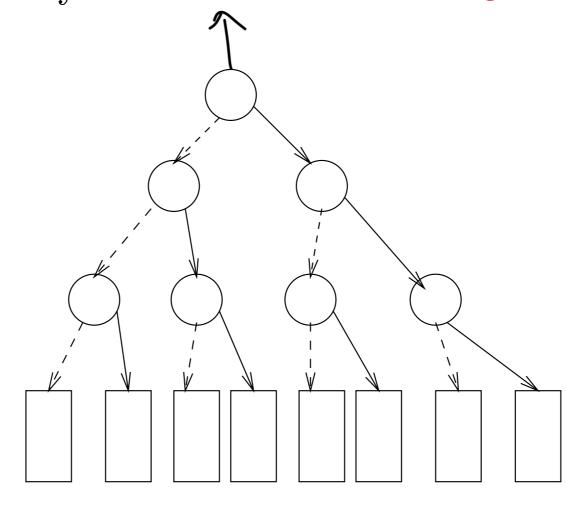

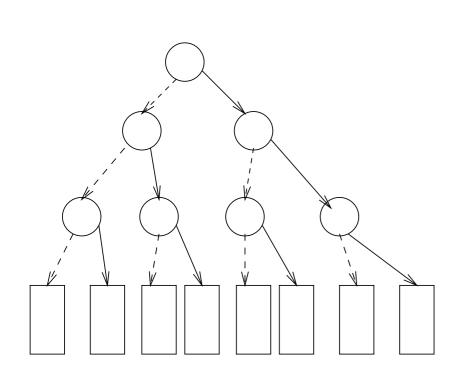

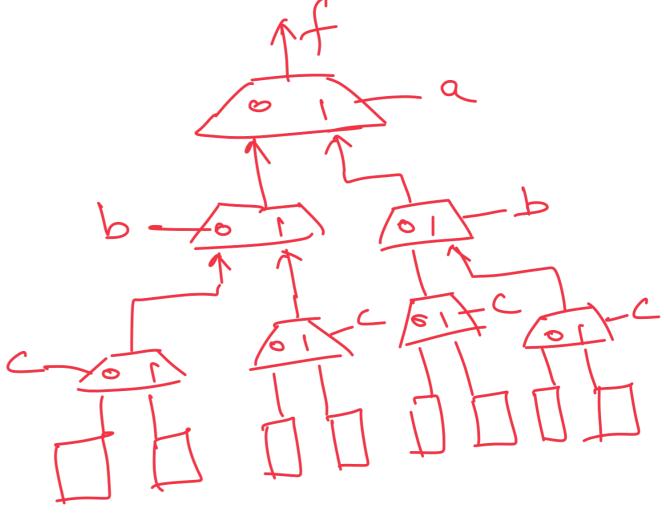

### MUXes as Universal logic

Truth Tables as Decision Trees

|                    |                      | ~ Diago! |  |

|--------------------|----------------------|----------|--|

| Truth Table versus | Binary Decision Tree | or )' () |  |

| 0             | b | 0 | f |

|---------------|---|---|---|

| $\frac{a}{a}$ |   | C |   |

| 0             | 0 | 0 | 0 |

| 0             | 0 | 1 | 0 |

| 0             | 1 | 0 | 0 |

| 0             | 1 | 1 | 1 |

| 1             | 0 | 0 | 0 |

| 1             | 0 | 1 | 1 |

| 1             | 1 | 0 | 1 |

| 1             | 1 | 1 | 1 |

|               |   |   | 1 |

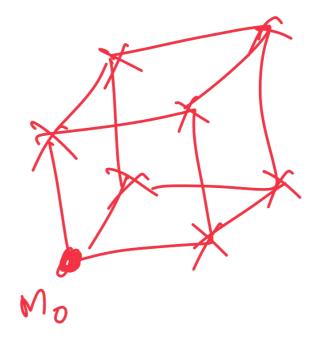

# Each node in the BDD (graph) is a Mux

From a truth-table to a BDD to only MUXes: universal logic!

This is what FPGAs are like....

### AND-XOR is universal logic

•

$$f = a + b = a \oplus b \oplus (a \cdot b)$$

•

$$f = \overline{a} = 1 \oplus a$$

$$xy + xy$$

$$= x \cdot 1 + 0 = x$$

$$x \cdot 0 + x \cdot 1 = x$$