## ECE/CS 5745/6745 Testing and Verification of Digital Circuits

Lecture Slides for ATPG, Redundancy & Test Generation, Reducing Test Generation Effort, and the Check-Point Theorems

**Priyank Kalla** Professor Electrical & Computer Engineering

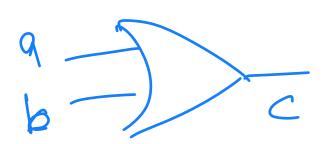

## **ATPG: Path Sensitization**

- First Try Single Path Sensitization

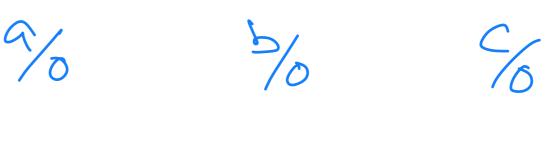

- D-calculus:  $v/v_f =$ fault-free/faulty value

- D=1/0,  $\overline{D} = 0/1$ , 0 = 0/0, 1 = 1/1

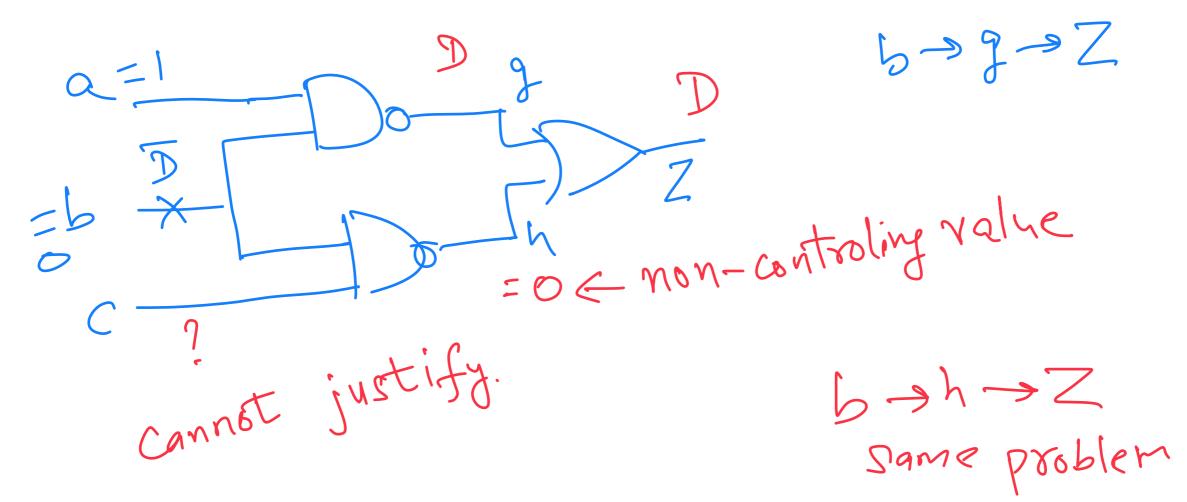

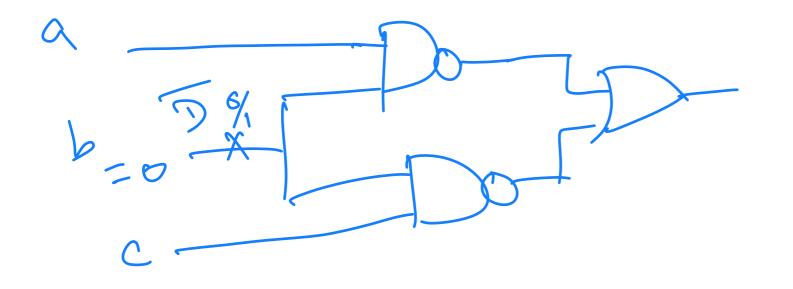

## **ATPG: Path Sensitization**

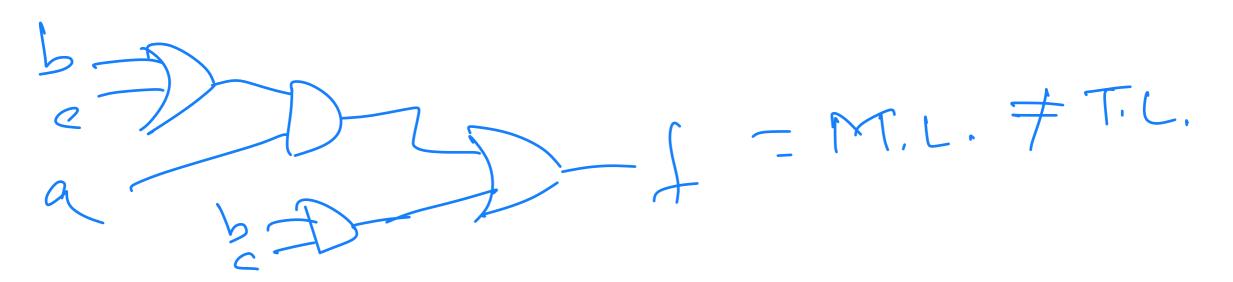

- Now Try Multi Path Sensitization

- D-calculus:  $v/v_f$  = fault-free/faulty value

- D=1/0,  $\overline{D} = 0/1$ , 0 = 0/0, 1 = 1/1

- Sometimes single-path sensitization works

- Sometimes multi-path sensitization works

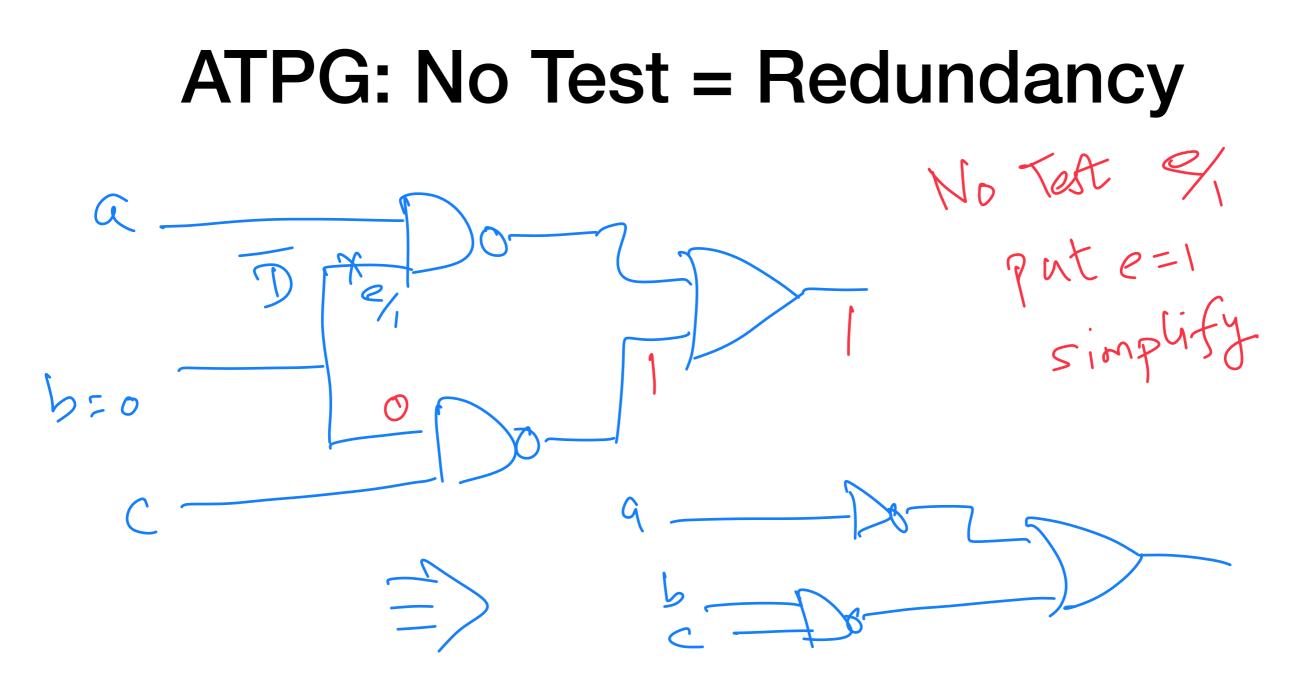

- Sometimes, test does not exist = redundancy

- Redundancy removal via s-a-f propagation

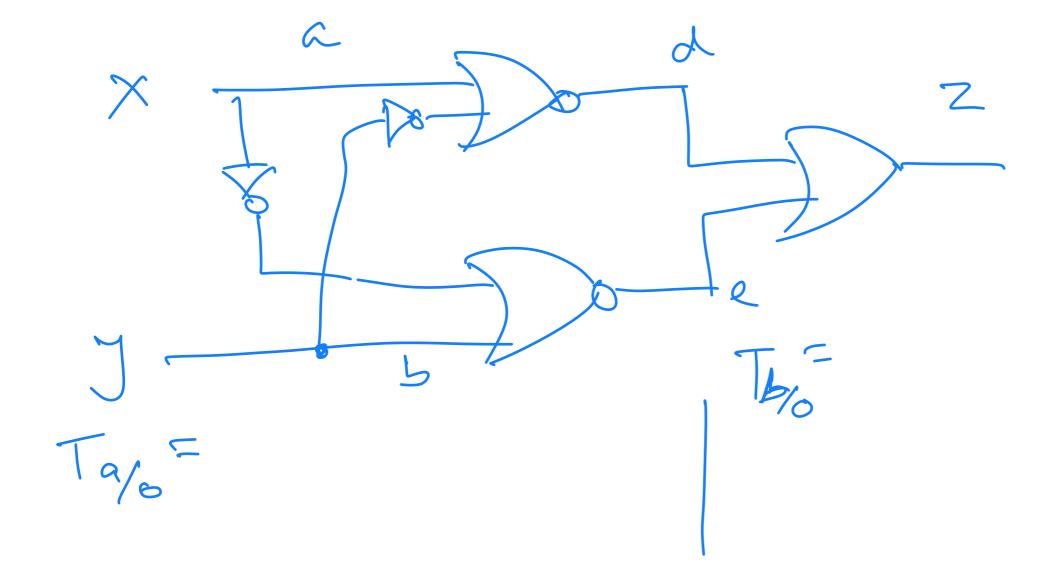

## **Testing using Boolean Difference**

- Let x be a PI, Z the PO. Prove that Test for x/1  $T_{x/1} = \overline{x} \cdot \frac{\delta Z}{\delta x} = \overline{x} \cdot [Z_x \oplus Z_{x'}]$

- Fault-free function Z, faulty function  $Z_f = Z(x = 1) = Z_x$

- $T_{x/1} = Z \oplus Z_x$  = miter between faulty and fault-free circuit Shannon's Expansion:  $Z = \chi Z_\chi + \chi Z_x$

Try = n Zr ( D Zz ( D Zr  $= Z_{\chi}(\chi \oplus i) \oplus \overline{\chi} Z_{\overline{\chi}}$ = ZZX DZZ  $= \frac{1}{2} \left[ \frac{1}{2} \oplus \frac{1}{2} \right] = \frac{1}{2} \frac{1}{2}$

Tx/m = x. 22/x

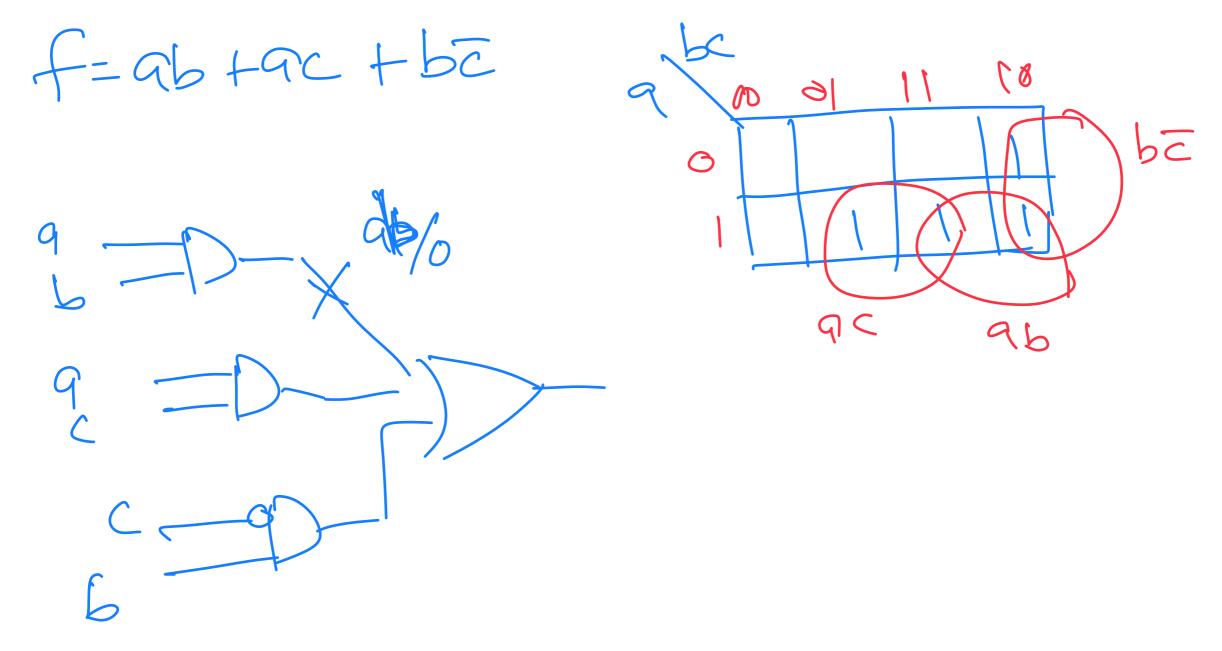

Z \ b/o: Z = (ab) + (bc) $= Z_b \oplus Z_b = \left[ (\overline{q} \cdot 1) + (\overline{q} \cdot c) \right] \oplus \left[ \overline{c} + \overline{c} \right]$  $=(\overline{q+c})\oplus I = (\overline{q+c}) = qc$ 99

· 12/0: 5. ac T5/: 5.90

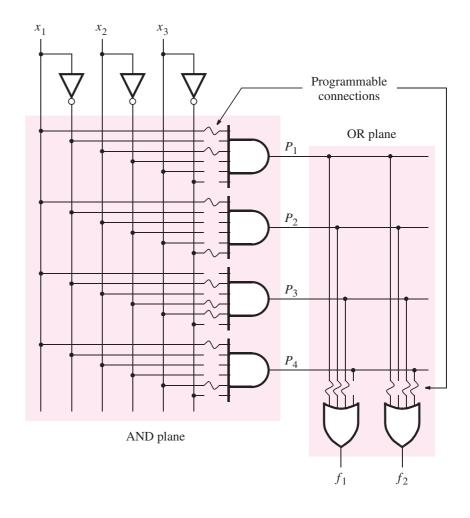

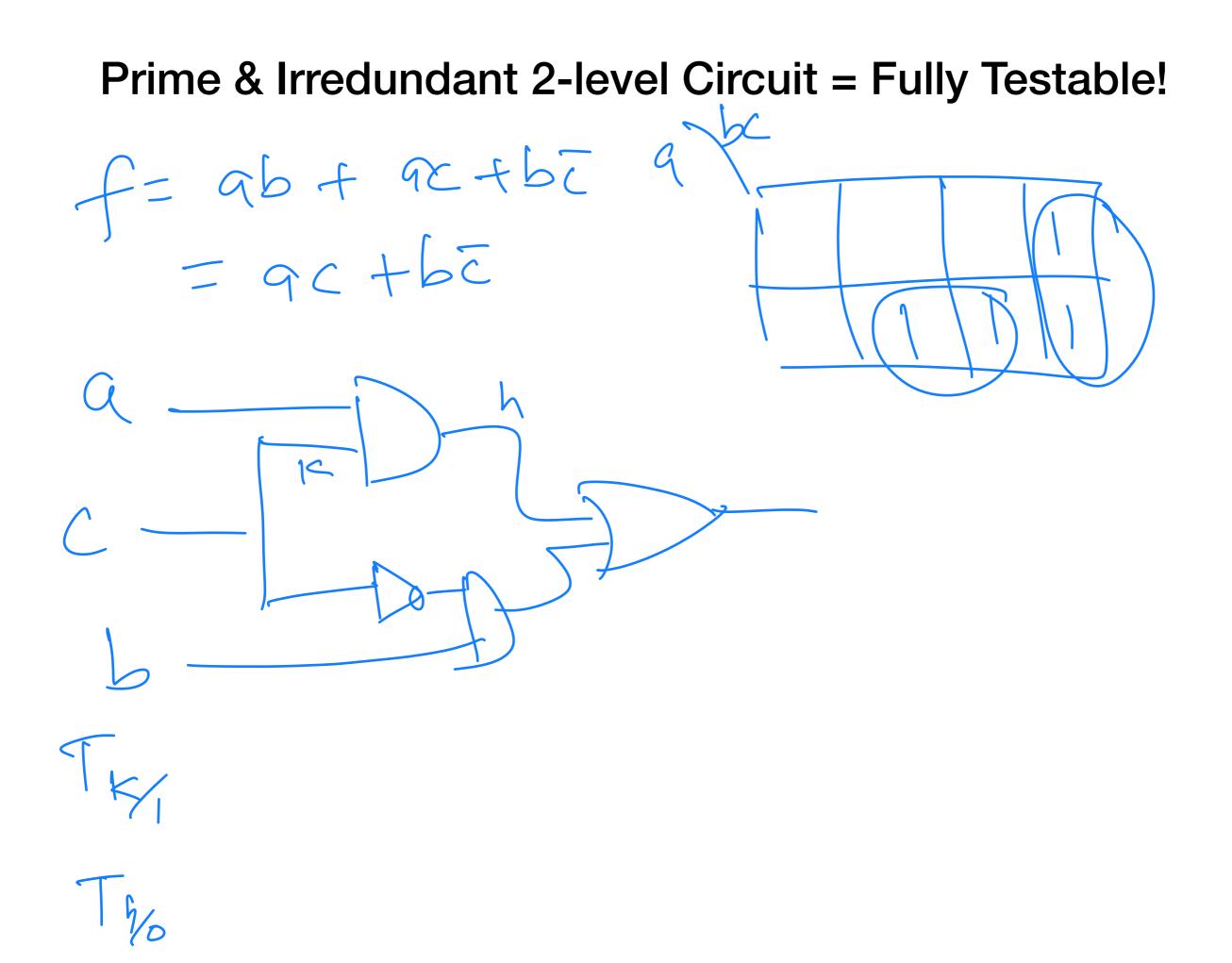

#### **Testability of Two-Level Logic Circuits**

- Two level logic = sum of product forms

- Implementation on Programmable Logic Array (PLA)

- Exact minimization using K-maps

- Make the cover prime and irredundant

- Minimize area, minimize delay, also fully testable circuit!

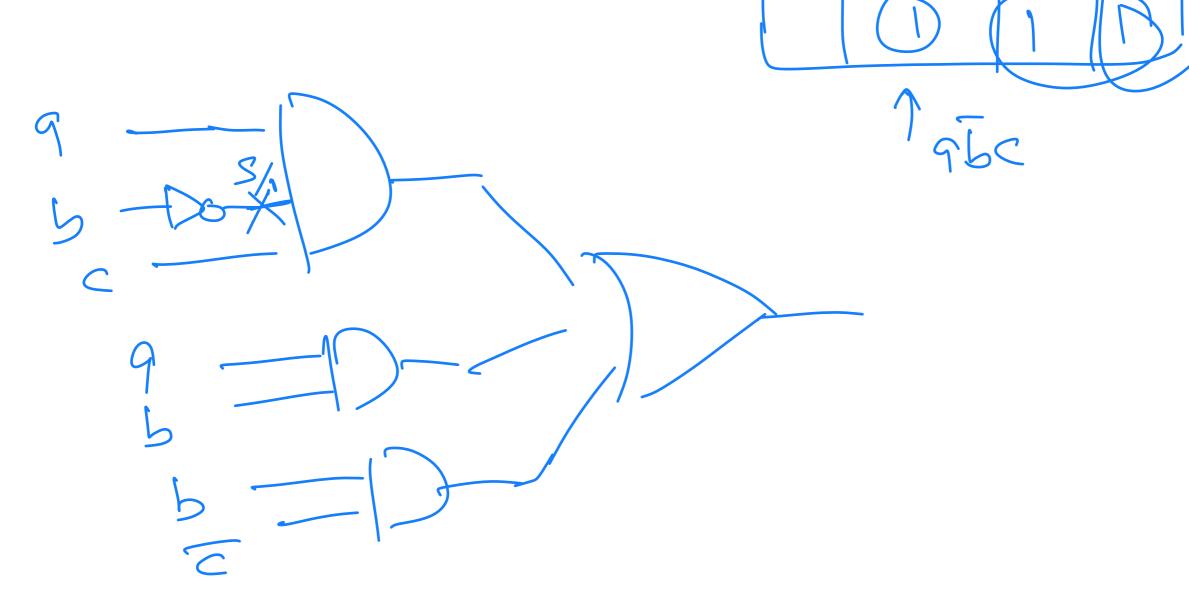

f = abc + abc + abc + abc= ab + ac + bc18 18 = a (btc) + bc = factored form - multi-level CKt.

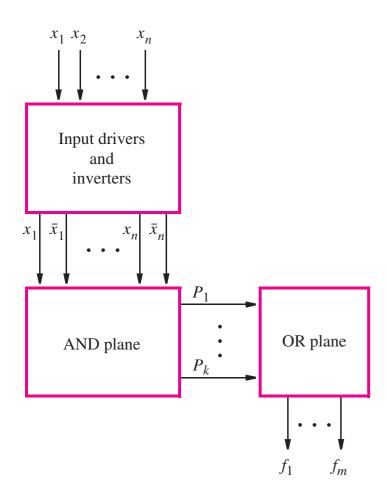

# Structure of PLAs

#### **ATPG: Redundant Cover**

• Redundant cube = untestable s-a-0 fault at AND-gate output

## **ATPG: Non-prime Cover**

• Non-prime cube = untestable s-a-1 fault at AND-gate input

## Fault Equivalence

- Two faults are functionally equivalent if their effect cannot be distinguished

- Detect only 1 out of ALL equivalent faults

- Infeasible to identify all functionally equivalent faults, so we try a simple problem of structural equivalence

## Fault Equivalence

- Two faults are functionally equivalent if their effect cannot be distinguished

- Detect only 1 out of ALL equivalent faults

- Infeasible to identify all functionally equivalent faults, so we try a simple problem of structural equivalence

7

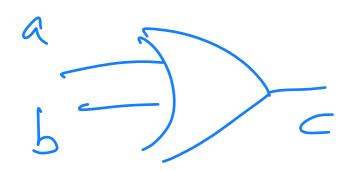

## **Structural Fault Equivalence**

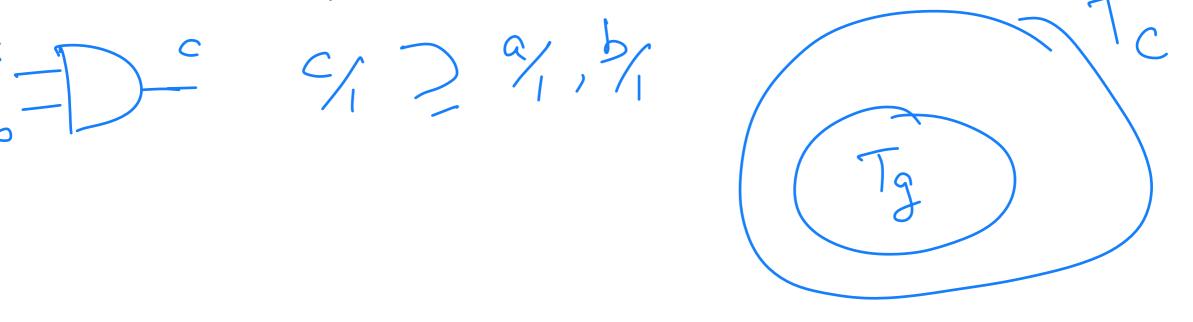

## Fault Dominance

- Let  $T_g$  be the set of all tests that detect fault g

- Fault *f* dominates fault *g* if  $Z_f(t) = Z_g(t) \quad \forall t \in T_g$

- Clearly  $T_f \supseteq T_g$ .

- If the goal is fault detection (and not fault distinguishing/diagnosis), then  $T_f$  is not needed,  $T_g$  suffices to detect fault f

C/0 > %, %