| Name: | Date: | Score: | / (75) |

|-------|-------|--------|--------|

|       |       |        |        |

# This lab MUST be done in your normal lab time— NO LATE LABS

Bring Textbook to Lab. You don't need to use your lab notebook, just fill in the blanks, you'll be graded when you're done.

A. Stolp, 4/17/00 rev,4/19/01

### University of Utah Electrical & Computer Engineering Department EE 2100 Experiment No. 13 JFET Transistor Introduction

## **Objectives**

- 1. Measure the characteristics of a junction-field-effect-transistor (JFET).

- 2. Construct and test a simple amplifier using the JFET.

# Check out from stockroom:

- Wire kit

- two 10x probes

- Multimeter

# Parts to be supplied by the student:

These items may be bought from stockroom.

- 270, 1 k, 1.5 k, 10 k, 100 k, & two 1 MΩ resistors + others you determine by design

- 0.1 to 1  $\mu$ F capacitor & two capacitors  $\ge$  10  $\mu$ F

- 2N5486 or 2N5248 JFET transistor (use data for 2N5486 in either case)

- Proto-board and wires

# **Experiment 1, JFET Characteristics**

**Data book:** Find a transistor data book or a data sheet (may be attached) that covers the 2N5486 JFET transistor. Find the important parameters for this transistor and record them in the blanks or in the table below.

- a. Determine the type of transistor (n or p-channel). \_

- b. Find the minimum and maximum  $V_t$  ( $V_{GS(off)}$ ), and note that the number is negative, confirming that the JFET is a depletion-mode device.

- c. Find the minimum and maximum  $I_{DSS}$ , which you'll be able to use in calculations.

- d. Find the forward transconductance (also called forward transfer admittance) measured with  $V_{GS} = 0 V (g_{m0}, g_{fs}, \text{ or } Y_{fs})$ . I'll refer to this as  $g_{m0}$  from now on.

|                  | Data sheet |     | Curve  | Manual      |  |

|------------------|------------|-----|--------|-------------|--|

|                  | min        | max | Tracer | Measurement |  |

| V <sub>t</sub>   |            |     |        |             |  |

| I <sub>DSS</sub> |            |     |        |             |  |

| g <sub>m0</sub>  |            |     |        |             |  |

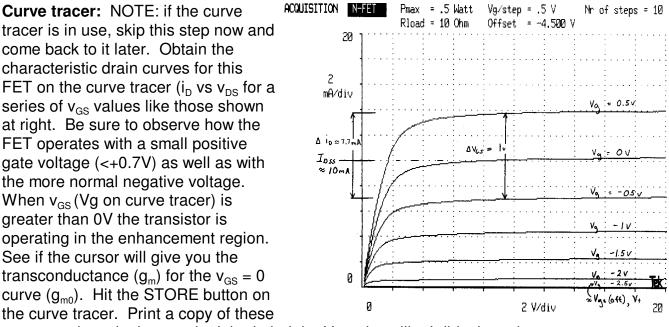

curves and staple them to the lab. Label the  $V_{gs}$  values like I did mine, above.

You're going to do something a little strange now, But it should demonstrate just how symmetric an FET is. Pull your JFET out of the connections and put it back in backwards--drain into the S terminal, source into the D terminal and the gate where it should be, in the G terminal. Take a second set of curves over the top of the set you just stored. Are they close to the same?\_\_\_\_\_ The only difference between the source and drain is that the FET will be designed so that the drain side has better heat dissipation characteristics.

If you were not able to find  $g_{m0}$  using the cursor, find it now from your printed curves. Refer to my example curves, above. (on my example curves:  $g_{m0} = \Delta i_D / \Delta v_{GS} = 7.7 \text{mA} / 1 \text{V} = 7.7 \text{mA} / \text{V} = 7700 \,\mu\text{mho}$ ). Find V<sub>t</sub> and I<sub>DSS</sub> for this FET from your printed curves. Note: There is a small chance that your JFET's V<sub>t</sub> is less than -4.5V. In that case, you won't be able to find V<sub>t</sub> here. Add all these values to the table on the first page.

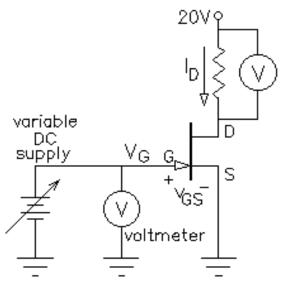

**Manual:** Build the circuit shown. This circuit will let you find the  $V_t (V_{GS(off)})$  and the transfer characteristic curve (saturation  $i_D vs v_{GS}$  like Fig 5.21c, p.378 in your book).

The voltmeter across the 1 k $\Omega$  resistor allows you to measure the drain current and the variable voltage supply allows you to vary the gate voltage. Note: You can use two separate outputs of the HP power supply or you can make the HP 33120 output DC by holding down the **Offset** button for 2 seconds. Just remember that it shows double its actual output voltage. ALSO: note the polarity of the DC supply.

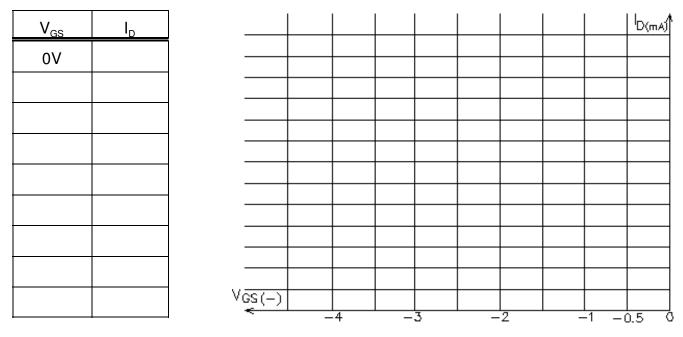

Turn the variable supply down to 0 V, and measure the drain current. Increase (make more negative) the variable supply voltage in small steps and record the data in the table. Take enough points to get a good plot. Pay particular attention to getting a good value for V<sub>t</sub> (V<sub>GS(off)</sub>), where I<sub>D</sub> = 0.

Plot an accurate transfer characteristic curve above. Determine a value for  $g_{m0}$  (the slope of the curve at  $v_{GS} = 0$ ,) from your data or plot (draw a tangent line and find its slope).

Enter your values of  $I_{DSS}$ ,  $V_t$ , and  $g_{m0}$  in the table on the first page. Compare the data-sheet numbers to those you found from the curve tracer and from your measurement circuit.

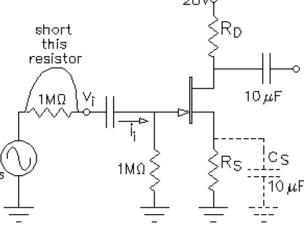

## **Experiment 2, JFET Amplifier**

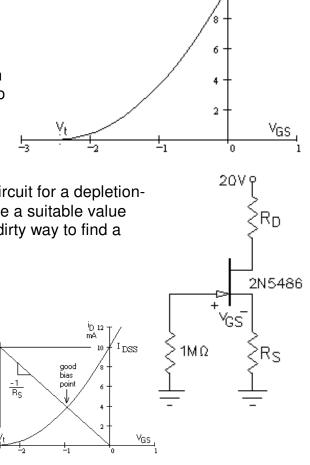

**Bias Design:** Figure 2 shows a simple self-bias circuit for a depletionmode FET.  $V_G = 0$  and  $V_{GS} = -V_S = -R_s I_D$ . Determine a suitable value for  $R_s$  from the data sheet numbers. A quick-and-dirty way to find a reasonable  $R_s$  is:

$$R_S = \frac{|V_t|}{I_{\text{DSG}}}$$

If you look at the curve at right you can see where this comes from. Calculate this once for the maximum  $|V_t|$  and  $I_{DSS}$  values from the data sheet and once again for the minimum values. Average your two  $R_s$  values to pick a standard resistor value for  $R_s$ . (Space is provided on the next page.)

mΑ

10

I DSS

$$R_{S} = \frac{|V_{t}|}{I_{DSS}}$$

For max  $|V_{t}|$  and  $I_{DSS}$ :

For min  $|V_t|$  and  $I_{DSS}$  :

Now that you have a value for  $R_s$ , calculate a minimum and a maximum  $I_D$ . Solve the equation below for  $I_D$ . Do it once for the maximum  $|V_t|$  and  $I_{DSS}$  values from the data sheet and once again for the minimum values. (I got about 2.9 & 8.1 mA, use those now if you want to make your own calculations later).

$$R_{S}^{2}I_{D}^{2} - 2[(V_{G}-V_{t})R_{S} + \frac{V_{t}^{2}}{2I_{DSS}}]I_{D} + (V_{G}-V_{t})^{2} = 0$$

You'd like to select a value for  $R_D$  so that  $V_D$  is about midway between  $V_{DD}$  and  $|V_t|$ . Try this for your two cases. Dismal results, aren't they? OK, select  $R_D$  so that in the worst case  $V_D$  is  $|V_t| + 2 V$  (I got about 1.5 k $\Omega$ , use that now if you want to make the calculations later).  $V_D$  must always be greater than  $|V_t|$ , no matter what the drain current is, or your JFET will fall out of saturation. (More space on next page.)

Notice that this design process is a pain because the characteristics can vary so much from part to part.

**Build amp:** Construct the amplifier shown without the bypass capacitor,  $C_s$ . Use the values of  $R_s$  and  $R_p$  that you selected earlier. Measure the DC  $V_s$  and  $V_p$  and calculate  $I_p$  from your measurements. Plot this bias point on your earlier transfer characteristic curve (the one you took manually), it should fall somewhere on the curve.

**Gain:** Adjust the signal generator to 1 kHz and apply a small input signal and observe both the input and output with the scope. Turn up the input signal until you can begin to see distortion in the output signal. The distortion you are looking for is an asymmetry in the sine wave. Turn the input signal back down to eliminate the distortion. Determine the voltage gain.

How does it compare to  $R_D/R_S$ ?

Not too close, is it? The gain of an FET amplifier is more difficult to determine than that of a BJT amplifier. It is also generally much lower for a similar circuit.

Add the bypass capacitor,  $C_s$ , lower the input and measure the gain again.

Now let's try something a little strange. In the first step you saw that this FET could also operate with small positive voltages on its gate, in the enhancement region of operation. What if you change the  $V_{GS}$  bias voltage to 0 V, that is, short  $R_s$ ? Think the amplifier will still work? Try it. You may have to turn down the input signal a little to eliminate distortion. What is the new voltage gain?

Why did it go up? (OK, with some FETs it doesn't go up— no, I don't know why, it *should* go up.)

Look back at the transfer characteristic curve you made, and see how the forward transconductance (the slope of the curve) is greater (steeper slope) at this new bias point than at the old one. With this new bias you get the maximum  $g_m (g_{m0})$ . Remove the short so  $R_s$  is back in the circuit.

**Input resistance:** Measure the output signal voltage. Remove the short across the 1 M $\Omega$  resistor (the one between the signal generator and the input capacitor). Measure the new output signal voltage. Notice how little it changed. What does this tell you about the input resistance of the FET amplifier?

**Frequency response:** Place the short back across the 1 M $\Omega$  resistor or you'll get a lousy frequency response. Turn up the input frequency to find the upper corner frequency ( $f_{CH}$ ).

### Conclusion Main Points of the lab

- 1. The large variability of V<sub>t</sub> and the inherent non-linearity of FETs makes it difficult to design a linear amplifier or a circuit with a large output swing. FETs are usually used as small signal amplifiers or switches.

- 2. FETs don't have very good gain

- 3. FETs have very high input impedance.

Get your lab instructor to check you off and grade this handout before you tear down your final circuit. No further conclusion is necessary.

### MAXIMUM RATINGS

| Rating                                                                | Symbol                            | Value       | Unit        |

|-----------------------------------------------------------------------|-----------------------------------|-------------|-------------|

| Drain-Gate Voltage                                                    | VDG                               | 25          | Vdc         |

| Reverse Gate-Source Voltage                                           | VGSR                              | 25          | Vdc         |

| Drain Current                                                         | ID                                | 30          | mAdc        |

| Forward Gate Current                                                  | IG(f)                             | 10          | mAdc        |

| Total Device Dissipation @ T <sub>C</sub> = 25°C<br>Derate above 25°C | PD                                | 310<br>2.82 | mW<br>mW/⁰C |

| Operating and Storage Junction<br>Temperature Range                   | T <sub>J</sub> , T <sub>stg</sub> | -65 to +150 | °C          |

ELECTRICAL CHARACTERISTICS (T<sub>A</sub> = 25°C unless otherwise noted.)

| Characteristic                                                                                                                                         |                            | Symbol               | Min                   | Тур | Мах                     | Unit         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------|-----------------------|-----|-------------------------|--------------|

| OFF CHARACTERISTICS                                                                                                                                    |                            |                      |                       |     |                         |              |

| Gate-Source Breakdown Voltage ( $I_G = -1.0 \ \mu Adc, V_{DS} = 0$ )                                                                                   |                            | V(BR)GSS             | - 25                  | _   | -                       | Vdc          |

| Gate Reverse Current<br>$(V_{GS} = -20 \text{ Vdc}, V_{DS} = 0)$<br>$(V_{GS} = -20 \text{ Vdc}, V_{DS} = 0, T_A = 100^{\circ}\text{C})$                |                            | IGSS                 |                       |     | - 1.0<br>- 0.2          | nAdc<br>μAdc |

| Gate Source Cutoff Voltage<br>(V <sub>DS</sub> = 15 Vdc, I <sub>D</sub> = 10 nAdc)                                                                     | 2N5484<br>2N5485<br>2N5486 | VGS(off)             | 0.3<br>- 0.5<br>- 2.0 |     | - 3.0<br>- 4.0<br>- 6.0 | Vdc          |

| ON CHARACTERISTICS                                                                                                                                     |                            |                      |                       |     | ·                       |              |

| Zero-Gate-Voltage Drain Current<br>(V <sub>DS</sub> = 15 Vdc, V <sub>GS</sub> = 0)                                                                     | 2N5484<br>2N5485<br>2N5486 | IDSS                 | 1.0<br>4.0<br>8.0     |     | 5.0<br>10<br>20         | mAdc         |

| SMALL-SIGNAL CHARACTERISTICS                                                                                                                           |                            |                      |                       | L   |                         | 4            |

| Forward Transfer Admittance<br>(V <sub>DS</sub> = 15 Vdc, V <sub>GS</sub> = 0, f = 1.0 kHz)                                                            | 2N5484<br>2N5485<br>2N5486 | Yfs                  | 3000<br>3500<br>4000  |     | 6000<br>7000<br>8000    | μmhos        |

| Input Admittance<br>(V <sub>DS</sub> = 15 Vdc, V <sub>GS</sub> $\pm$ 0, f = 100 MHz)<br>(V <sub>DS</sub> = 15 Vdc, V <sub>GS</sub> = 0, f = 400 MHz)   | 2N5484<br>2N5485, 2N5486   | Re(y <sub>is</sub> ) | _                     |     | 100<br>1000             | µmhos        |

| Output Admittance<br>( $V_{DS} = 15 \text{ Vdc}, V_{GS} = 0, f = 1.0 \text{ kHz}$ )                                                                    | 2N5484<br>2N5485<br>2N5486 | Yos                  |                       |     | 50<br>60<br>75          | µmhos        |

| Output Conductance<br>( $V_{DS} = 15 \text{ Vdc}, V_{GS} = 0, f = 100 \text{ MHz}$ )<br>( $V_{DS} = 15 \text{ Vdc}, V_{GS} = 0, f = 400 \text{ MHz}$ ) | 2N5484<br>2N5485, 2N5486   | Re(y <sub>OS</sub> ) |                       |     | 75<br>100               | µmhos        |

| Forward Transconductance ( $V_{DS} = 15 \text{ Vdc}, V_{GS} = 0, \text{ f} = 100 \text{ MHz}$ )                                                        | 2N5484                     | Re(y <sub>fs</sub> ) | 2500                  | _   | _                       | μmhos        |

| $(V_{DS} = 15 \text{ Vdc}, V_{GS} = 0, f = 400 \text{ MHz})$                                                                                           | 2N5485<br>2N5486           |                      | 3000<br>3500          |     |                         |              |

### MOTOROLA SEMICONDUCTORS

#### SMALL-SIGNAL DEVICES